VMEbus Interface w/DMA

INSTRUCTION MANUAL

May 22, 2001

© 1990, 1991, 1992, 1996, 2000, 2001 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

# CONTENTS

| FEATURES AND APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         | ]                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------|

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | 1                                                                                    |

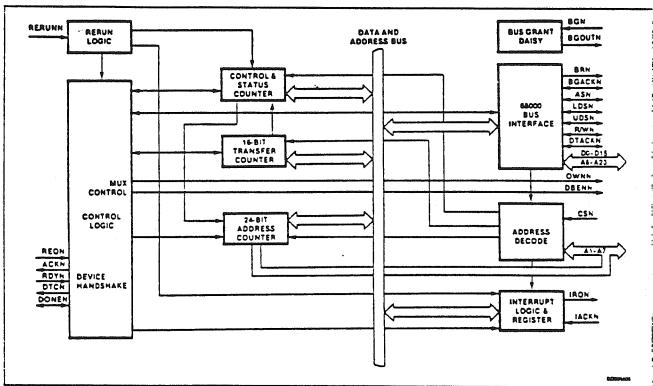

| SIMPLIFIED BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         | 2                                                                                    |

| ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | 2                                                                                    |

| UNPACKING AND INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | ,                                                                                    |

| UNFACKING AND INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                      |

| SWITCH AND STRAP SELECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                      |

| Device Address Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |                                                                                      |

| VME Bus Grant Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                      |

| Data Storage Format Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |                                                                                      |

| FRONT PANEL LEDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |                                                                                      |

| External Trigger In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |                                                                                      |

| Reset Button                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         | . 7                                                                                  |

| Tweet Button                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • • • • • • • • • • • • • • • • • • • • | . 4                                                                                  |

| 2917 REGISTER DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         | . 4                                                                                  |

| DMA CONTROLLER REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         | . 4                                                                                  |

| Channel Status/Error Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |                                                                                      |

| Device/Operation Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         | . 6                                                                                  |

| Sequence/Channel Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         | 7                                                                                    |

| Memory Transfer Count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         | ٠.<br>اع                                                                             |

| Memory Address Counter Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         | . S                                                                                  |

| Memory Address Counter High (MACHI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | . Ω                                                                                  |

| 110mory radioss codifici flight (11110fli)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | . 0                                                                                  |

| Memory Address Counter Low (MACLO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         | Я                                                                                    |

| Memory Address Counter Low (MACLO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         | . 8                                                                                  |

| Memory Address Counter Low (MACLO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |                                                                                      |

| Memory Address Counter Low (MACLO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         | . 9                                                                                  |

| Memory Address Counter Low (MACLO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         | . 9<br>. 9                                                                           |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS  Interrupt Control Registers  Interrupt Vector Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | . 9<br>. 9<br>10                                                                     |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS  Interrupt Control Registers  Interrupt Vector Registers  2917 ON-BOARD REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | . 9<br>. 9<br>10                                                                     |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS  Interrupt Control Registers  Interrupt Vector Registers  2917 ON-BOARD REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | . 9<br>. 9<br>10                                                                     |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers 2917 ON-BOARD REGISTERS Address Modifier Register                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | . 9<br>. 9<br>10<br>10                                                               |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register                                                                                                                                                                                                                                                                                                                                                                             |                                         | . 9<br>. 9<br>10<br>10<br>10                                                         |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Address Register                                                                                                                                                                                                                                                                                                                                             |                                         | . 9<br>. 9<br>10<br>10<br>10<br>11<br>14                                             |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Address Register Command Word Count Register                                                                                                                                                                                                                                                                                                                 |                                         | . 9<br>. 9<br>10<br>10<br>11<br>14<br>14                                             |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Register Command Memory Address Register Command Word Count Register Service Request Register                                                                                                                                                                                                                                                                |                                         | . 9<br>. 9<br>10<br>10<br>11<br>14<br>14<br>14                                       |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Register Command Memory Address Register Command Word Count Register Service Request Register Data Low Register                                                                                                                                                                                                                                              |                                         | . 9<br>. 9<br>10<br>10<br>11<br>14<br>14<br>14<br>15                                 |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Address Register Command Word Count Register Service Request Register Data Low Register Data High Register                                                                                                                                                                                                                                                   |                                         | . 9<br>. 9<br>10<br>10<br>11<br>14<br>14<br>15<br>15                                 |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Address Register Command Word Count Register Service Request Register Data Low Register Data High Register Control Status Register                                                                                                                                                                                                                           |                                         | . 9<br>. 9<br>10<br>10<br>11<br>14<br>14<br>15<br>15                                 |

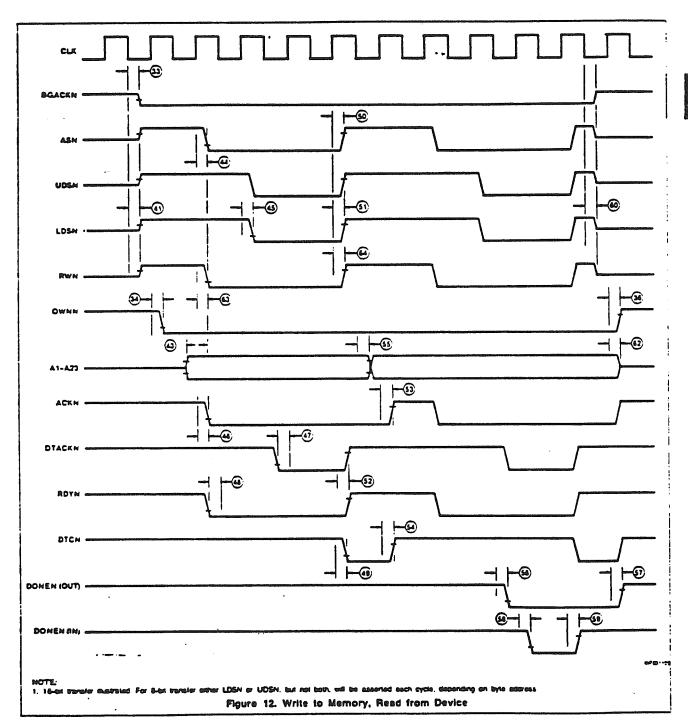

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Address Register Command Word Count Register Service Request Register Data Low Register Data High Register Control Status Register  2917 OPERATING MODES                                                                                                                                                                                                     |                                         | . 9<br>. 9<br>. 10<br>10<br>11<br>14<br>14<br>15<br>15<br>15                         |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Address Register Command Word Count Register Service Request Register Data Low Register Data High Register Control Status Register  2917 OPERATING MODES Slave Single Transfers                                                                                                                                                                              |                                         | . 9<br>. 9<br>. 10<br>10<br>11<br>14<br>14<br>15<br>15<br>15<br>17                   |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Address Register Command Word Count Register Service Request Register Data Low Register Data High Register Control Status Register  2917 OPERATING MODES Slave Single Transfers Programmed Transfer Read Operation (F16=0: F8=0)                                                                                                                             |                                         | . 9<br>. 9<br>10<br>10<br>11<br>14<br>14<br>15<br>15<br>17<br>17                     |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | . 9<br>. 9<br>. 10<br>10<br>10<br>11<br>14<br>14<br>15<br>15<br>15<br>17<br>17<br>17 |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | . 9<br>. 9<br>. 10<br>10<br>10<br>11<br>14<br>14<br>15<br>15<br>17<br>17<br>17<br>18 |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS Interrupt Control Registers Interrupt Vector Registers  2917 ON-BOARD REGISTERS Address Modifier Register Command Memory Register Command Memory Address Register Command Word Count Register Service Request Register Data Low Register Data High Register Control Status Register  2917 OPERATING MODES Slave Single Transfers Programmed Transfer Read Operation (F16=0: F8=0) Programmed Transfer Write Operation (F16=1: F8=0) Programmed Transfer Control Operation (F16=X: F8=1) Slave Block Transfers |                                         | . 9<br>. 9<br>. 10<br>10<br>11<br>14<br>14<br>15<br>15<br>17<br>17<br>17<br>18<br>18 |

| Memory Address Counter Low (MACLO)  BUS INTERRUPT REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | . 9<br>. 9<br>. 10<br>10<br>11<br>14<br>14<br>15<br>15<br>17<br>17<br>17<br>18<br>18 |

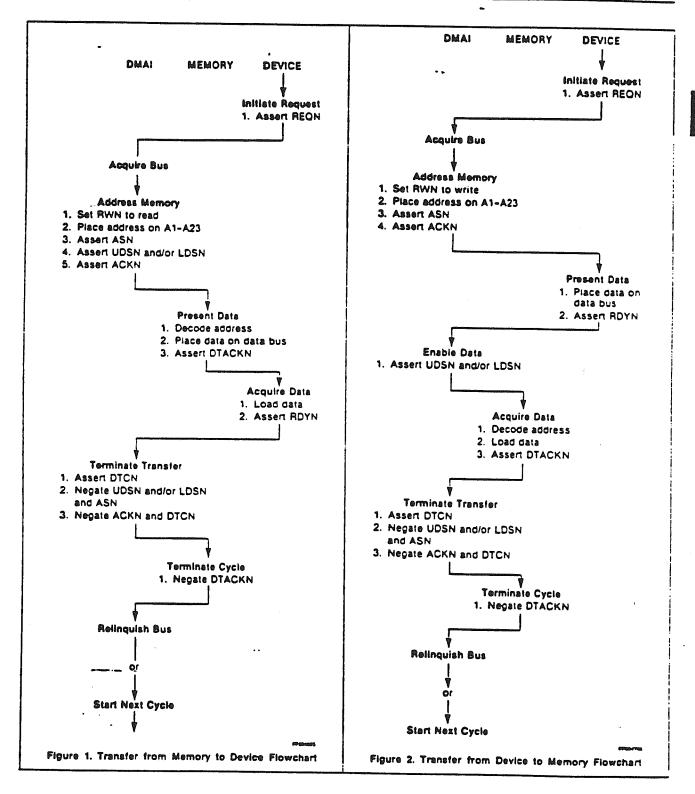

| DMA Transfers                                                                                                                                  |                                   |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|--|--|

| DMA Single Transfer Write/Read Operation  DMA Block Transfers                                                                                  |                                   |  |  |  |  |  |  |  |

| DMA Block Transfer Write/Read Operation                                                                                                        |                                   |  |  |  |  |  |  |  |

| BLOCK MODES  Q-STOP Block Transfer  Q-IGNORE Block Transfer  Q-REPEAT Block Transfer  Q-SCAN Block Transfer                                    |                                   |  |  |  |  |  |  |  |

| 2917/3922 INTERCONNECTION BUS                                                                                                                  |                                   |  |  |  |  |  |  |  |

| FEATURES AND OPERATION Address Selection Registers Status Register                                                                             |                                   |  |  |  |  |  |  |  |

| MODEL 3922 CRATE CONTROLLER  LAM Register                                                                                                      |                                   |  |  |  |  |  |  |  |

| 3922 FRONT PANEL Switches LEDs LEMOs                                                                                                           |                                   |  |  |  |  |  |  |  |

| INSTALLING THE CRATE CONTROLLER  Operating Option Selections  Installing the 3922  Front Panel Set-up                                          |                                   |  |  |  |  |  |  |  |

| 2917 REGISTER LAYOUT                                                                                                                           |                                   |  |  |  |  |  |  |  |

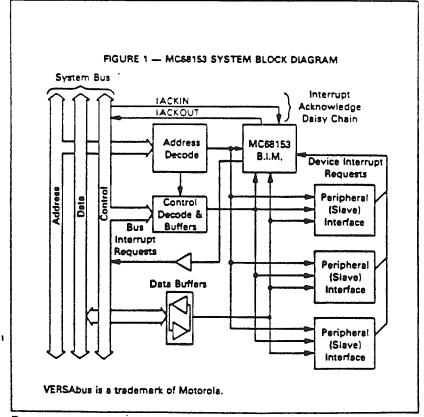

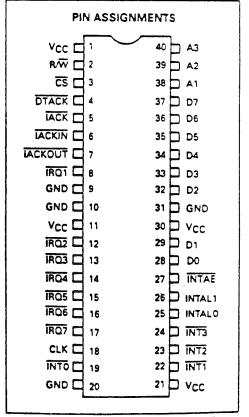

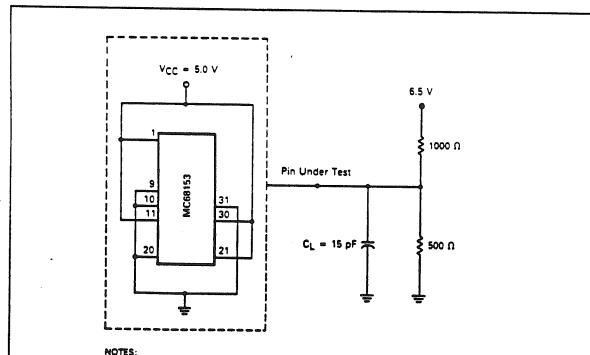

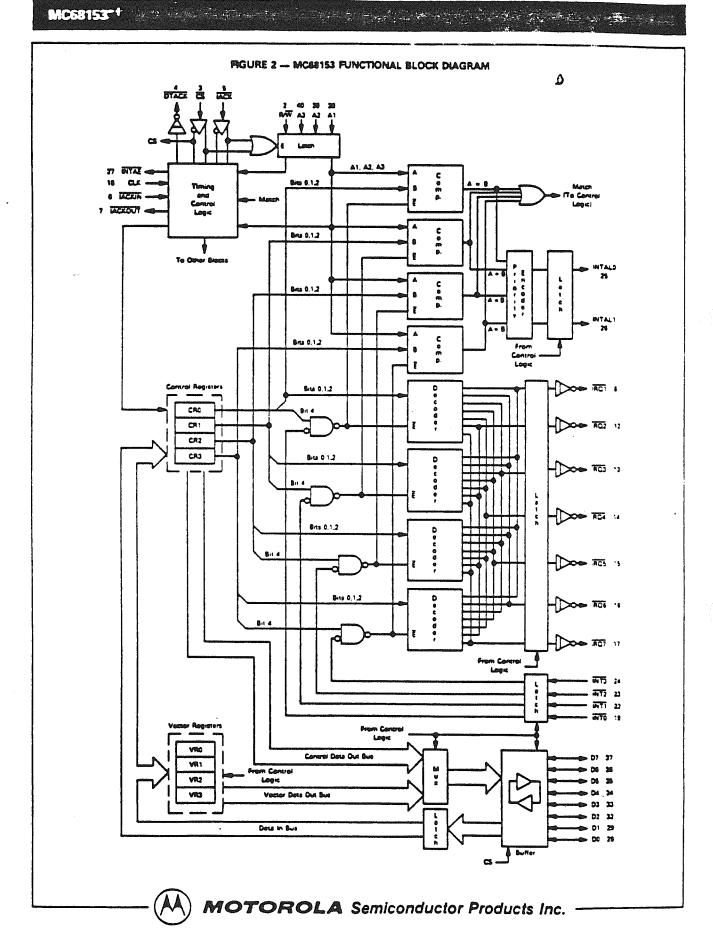

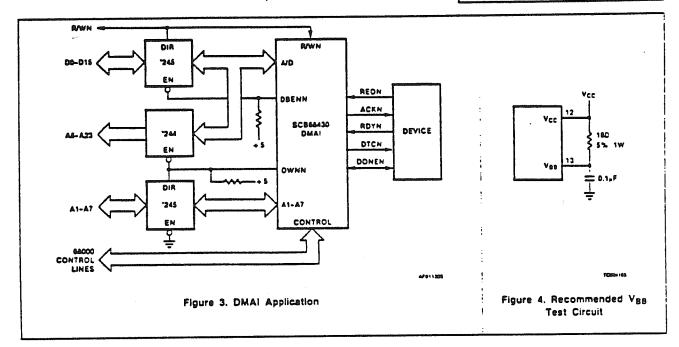

| APPENDIX A - Motorola MC68153 Bus Interrupter Chip Data Sheets APPENDIX B - Signetics SCB68430 Direct Memory Access Interface Chip Data Sheets |                                   |  |  |  |  |  |  |  |

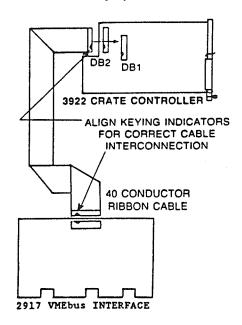

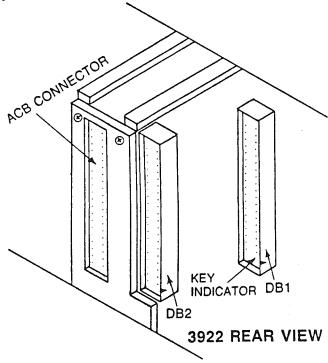

| Figure 1 - 3922 K-Bus Connection                                                                                                               |                                   |  |  |  |  |  |  |  |

| Schematic Drawing # 086101-C-6033                                                                                                              | See Reply Card Following Warranty |  |  |  |  |  |  |  |

|                                                                                                                                                |                                   |  |  |  |  |  |  |  |

Warranty

# VME Interface for the 3922 Controller

# Allows a computer VME bus to host up to eight 3922s

2917

#### **Features**

- Provides dedicated VMEbus interface

- Used with 3922 parallel-bus crate controllers

- Supports DMA transfers

- Controls up to eight CAMAC crates

- Bus lengths up to 90 meters (300 feet)

- RS-485 balanced-line signaling between the 2917 and 3922s for high noise immunity

- · Throughput up to 1 megabyte per second

- 16 kilobyte command list memory

- Full VMEbus master capabilities

- Supports 16-bit VMEbus transfers

- Flexible interrupt structure

# **Typical Applications**

- Integrate CAMAC with VME systems

- · General-purpose data acquisition and control

- Laboratory automation

- · Industrial process control

- Flight simulation systems

# General Description (Product specifications and descriptions subject to change without notice.)

The 2917 is a computer-bus adapter for use with computers incorporating the VMEbus. The 2917 provides the interface between the VMEbus and as many as eight CAMAC crates using the 3922 Parallel Bus Crate Controller. Connection is made via a parallel bus that is a 40-conductor twisted-pair ribbon cable. Bus lengths must be ordered separately. Signaling on the parallel bus is accomplished using RS-485 balanced line drivers and receivers, which gives high noise immunity and allows an overall cable distance between the 2917 and the last 3922 of up to 90 meters (300 feet). The last 3922 on the parallel bus is terminated with a termination card provided with the 3922.

Data throughput rates for a 16-bit data transfer using a 5 meter cable between the 2917 and a 3922 is 920 kbytes per second for CAMAC double-buffer read operations. 890 kbytes can be achieved with CAMAC write operations.

CAMAC operations are executed from a 16-bit x 8192 word on-board command-list memory. CAMAC data to and from the VMEbus can be transferred with the 2917 acting as either bus master or slave. All data transfers between the 2917 and the VMEbus are 16 bits wide. 32-bit addresses are generated by the 2917 during DMA transfers. Block transfers based on the CAMAC Q-response are supported.

The 2917 can generate an interrupt on the VMEbus when a CAMAC Look-At-Me (LAM) occurs or when the entire command list has been executed. The request level at which the interrupt is made is programmable from VMEbus, as is the generated interrupt vector.

# **Power Requirements**

+5 volts:

4020 mA

# **Ordering Information**

Model 2917-Z1A

VMEbus Interface to the model 3922 crate controller, with DMA

#### **Associated Products**

Model 3922-Z1B

Parallel Bus Crate Controller

Model 5843-Txyz

Bus Interface Cable (one required for each 3922)

# UNPACKING AND INSTALLATION

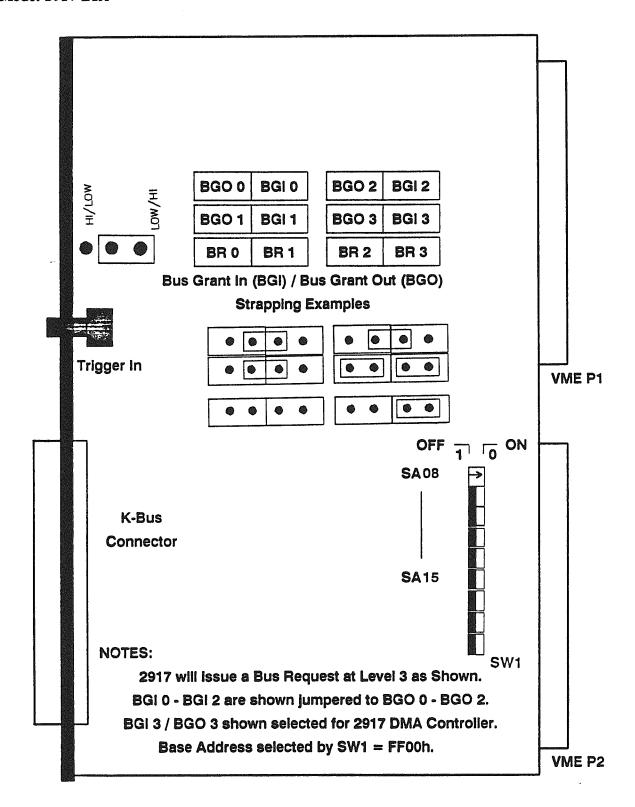

The Model 2917 is shipped in a antistatic bag within a Styrofoam packing container. Carefully remove the module from its static-proof bag and set the various options to conform to the operating environment. The default settings on the 2917 are as follows: base address set to \$FF00 HEX, VME Bus Request set level three, and Data Storage Format set to LOW/HI. Figure 3 shows the location of components affected by option choices.

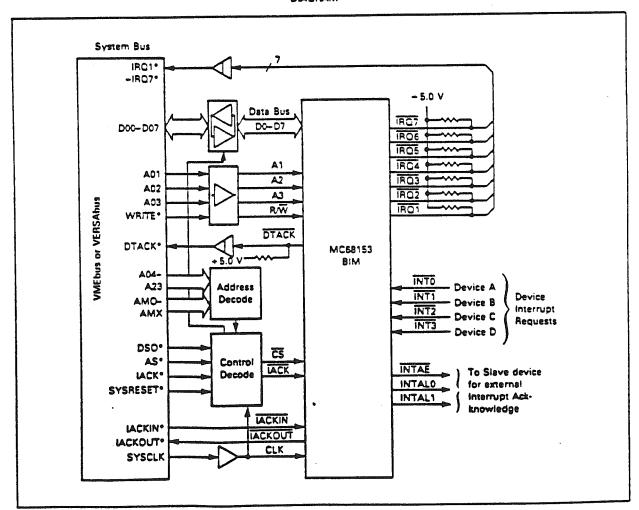

The 2917 is a VME "B" size module that requires both P1 and P2 VME backplane connectors. The selected VME slot that the 2917 will reside in requires the Bus Request (BR) and Interrupt Acknowledge (IACK) straps be removed for proper VME bus operation. Any empty slots between the 2917 and slot one should have their BR and IACK straps loaded. Connect the 2917 front panel K-Bus connector to the 3922 crate controllers with the last 3922 having a termination card connected. Refer to the 3922 Crate Controller section for more information on the 3922.

# **SWITCH AND STRAP SELECTION**

#### <u>Device Address Selection</u>

The 2917 resides in the short I/O address space of the VME bus and responds to both short I/O Address Modifier Codes - 29 HEX (Short Non-Privileged Access) and 2D HEX (Short Supervisory Access). The switches SA15 through SA08 determine the base address of the 2917. The 2917 must allocate the 256 word location in the short I/O address space. The default base address setting is FF00 HEX.

# WHEN SELECTING A BASE ADDRESS, CARE SHOULD BE TAKEN TO AVOID ADDRESSES ASSIGNED TO OTHER DEVICES IN THE SHORT I/O ADDRESS SPACE.

The bit pattern for the base address is shown below:

| 15       | 14       | 13       | 12       | 11       | 10       | 09       | 80       | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----------|----------|----------|----------|----------|----------|----------|----------|----|----|----|----|----|----|----|----|

| SA<br>15 | SA<br>14 | SA<br>13 | SA<br>12 | SA<br>11 | SA<br>10 | SA<br>09 | SA<br>08 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Bits 15 through 08 are user selectable via the address switches SA15-SA08.

Bit 07 is set to zero.

Bits 06 through 00 are set to "0" to indicate a block of 256 words.

Refer to Figure 3 on page 38 for switch location and switch settings.

### VME Bus Grant Selection

The 2917 can be selected for all four Bus Request (BR) settings. The 2917 uses the BR signals to become a VME master for DMA operations. The BR straps on the VME backplane need to be removed from the slot that the 2917 occupies. The default setting is BR #3. Refer to Figure 3 on page 38 for location of Bus Request straps and settings.

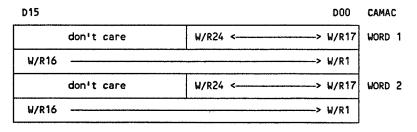

# **Data Storage Format Selection**

The 2917 has an option to select the order in which a 24-bit CAMAC word is fetched/stored. A strap on the 2917 selects this option with the default set to LOW/HI. This setting will first access the lower 16-bit CAMAC word then the upper 8-bit CAMAC word. Refer to the DMA section for more operating details, also refer to Figure 3 on page 37 for location and strap selection.

# FRONT PANEL LEDS

ADD\_REC: This LED indicates when the 2917 is being addressed from the VME bus.

RUN: This LED indicates that the 2917 is running a command list.

command that was executed.

M2,M1: These two LEDs indicate the current CAMAC operating mode. They reflect bits 4 and 3 in the current Mode word of the Command List.

LAM: This LED indicates that one or more crates connected to the 2917 has a LAM set and is need of service.

NO-X: This LED indicates the status of the CAMAC X-response from the last CAMAC command that was executed.

NO-Q: This LED indicates the status of the CAMAC Q-response from the last CAMAC

ERR: This bit indicates that the last CAMAC operation had ended in an error condition.

# External Trigger In

The 2917 has a front panel Trigger-In input to start the execution of the Command List. This is the same thing as setting the GO bit in the CSR. The trigger pulse is a low-true signal requiring a minimum of 50 ns pulse width. The DMA bit and/or DIR bit in the CSR must be set to the desired setting prior to the Trigger-In input.

### Reset Button

The front panel Reset button will reset the 2917 to a power-up condition. The command memory data will retain the previous stored data.

# 2917 REGISTER DESCRIPTION

# DMA CONTROLLER REGISTER

The DMA Controller has 12 8-bit registers that need to be programmed prior to any DMA transfer on the VMEbus. These 12 registers can be grouped as six 16-bit word registers for ease of programming. Programming information on the DMA controller can be found below in the

register descriptions and also in the Technical Specifications included in Appendix A of this manual.

# Channel Status/Error Register

The Channel Status/Error Register (CSER) is used to monitor current status and error conditions of the DMA controller. Prior to starting a DMA transfer, bits #15, #13 and #12 must be cleared to zero. A register layout and description of the Channel Status/Error Register is given below:

| 15                   | 14       | HANNEL<br>13         | STATU<br>12 | S REGIS              | STER (1  | CSR)<br>09 | 08       | 07       | 06          | CHANI<br>05 | NEL ERF | OR REC | SISTER<br>02 | (CER)<br>01 | 00 |

|----------------------|----------|----------------------|-------------|----------------------|----------|------------|----------|----------|-------------|-------------|---------|--------|--------------|-------------|----|

| COC<br>0=NO<br>1=YES | N/U<br>0 | NDT<br>0=NO<br>1=YES | 1           | ACT<br>0=NO<br>1=YES | N/U<br>O | N/U<br>0   | RDY<br>0 | N/U<br>0 | N/U<br>O    | N/U<br>0    |         | ERF    | OR COL       | DE .        |    |

|                      |          | D08(E                | O) OFF      | SET = \$             | 00       | D.         | 16 OFF:  | SET = 9  | <b>5</b> 00 | D08(E       | 0) OFF  | SET =  | \$01         |             |    |

| BIT#    | MNEMONIC | DESCRIPTION                                                                                                                                                                                             |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | coc      | Channel Operation Complete. When this bit is set, a DMA transfer has completed whether successful or not. This bit must be cleared before another transfer is started.                                  |

| 14      | N/U      | Not used. Read as zero.                                                                                                                                                                                 |

| 13      | NDT      | Normal Device Terminate. When this bit is set, the command list has aborted. Check the 2917 on-board CSR register for the abort condition. This bit must be cleared before another transfer is started. |

| 12      | ERR      | Error. Error is set when the transfer termination was due to an error. Read the Channel Error Register to determine the cause. This bit must be cleared before another transfer is started.             |

| 11      | ACT      | Channel Active. This bit is set when the channel has been started and remains set until the operation is terminated.                                                                                    |

| 10, 9   | N/U      | Not used. Read as zeros.                                                                                                                                                                                |

| 8       | RDY      | Ready Input State. This bit indicates the 2917 is ready. This bit is always read as a zero.                                                                                                             |

| 7, 6, 5 | N/U      | Not used. Read as zeros.                                                                                                                                                                                |

4-0 ERR CODE

Error Code. This Error Code indicates the source of the error when indicated by CSR #12. These Error Code bits are clear when the CSR #12 is cleared.

### ERROR CODES

00000 = No Error 01001 = Bus Error

10001 = Software Abort

# **Device/Operation Control Register**

The Device/Operation Control Register (DOCR) is used to select operating conditions of the DMA Controller. This register must be written to, before a transfer is started. A register layout and description of the Device/Operation Control Register is given below:

|                       | Di  | EVICE | CONTROL | REGIS       | STER | (DCR) |     |     |        |             | OPERA   | TION C | ONTROL | REGIS | TER (OC |

|-----------------------|-----|-------|---------|-------------|------|-------|-----|-----|--------|-------------|---------|--------|--------|-------|---------|

| 15                    | 14  | 13    | 12      | 11          | 10   | 09    | 08  | 07  | 06     | 05          | 04      | 03     | 02     | 01    | 00      |

| EXT<br>REQ            | N/U | N/U   | N/U     | OCR<br>BITS | N/U  | N/U   | N/U | DIR | N/U    | OPER<br>SIZ |         | N/U    | N/U    | N/U   | N/U     |

| MODE                  | 0   | 1     | 1       | (5:4)       | 0    | 0     | 0   |     | 0      | 1           |         | 0      | 0      | 1     | 0       |

| D08(EQ) OFFSET = \$04 |     |       |         |             |      |       |     |     | D08(F0 | ) OFF       | SFT = ' | \$05   |        |       |         |

D16 OFFSET = \$04

| BIT#   | MNEMONIC     | DESCRIPTION                                                                                                                                                                       |

|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | EXT REQ MODE | External Request Mode. This bit must be written with a one, the 2917 only can operate in Cycle Steal mode. A value of zero equals Burst mode. This is not a valid operating mode. |

| 14     | N/U          | Not used. Read as zero.                                                                                                                                                           |

| 13, 12 | N/U          | Not used. Read as ones.                                                                                                                                                           |

| 11     | OCR(5:4)     | This bit is set if either bit #4 or #5 in the Operation Control Register is set to a one.                                                                                         |

| 10-8   | N/U          | Not used. Read as zeros.                                                                                                                                                          |

| 7      | DIR          | Direction:<br>0 = Memory to 2917 (CAMAC writes)<br>1 = 2917 to Memory (CAMAC reads)                                                                                               |

| 6      | N/U          | Not used. Read as zero.                                                                                                                                                           |

5, 4 SIZE

**Operand Size.** Operand size must be set 01. The 2917 only transfers words.

| Bits 5,4 | Size        |

|----------|-------------|

| 0 0 =    | Byte        |

| 0 1 =    | Word        |

| 1 0 =    | Long Word   |

| 1 1 =    | Double Word |

| 3, | 2    | N/U | Not | used. | Read | as | zeros. |

|----|------|-----|-----|-------|------|----|--------|

| 1  | w.c. | N/U | Not | used. | Read | as | one.   |

| 0  |      | N/U | Not | used. | Read | as | zero.  |

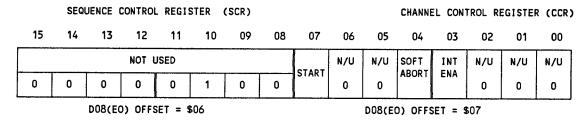

# Sequence/Channel Control Register

The Sequence/Channel Control Register (SCCR) is used to initiate the start of a DMA operation or to abort a DMA operation. A register layout and description of the Sequence/Channel Control Register is given below:

D16 OFFSET = \$06

| BIT#  | MNEMONIC   | DESCRIPTION                                                                                                                                                                                       |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-11 | N/U        | Not used. Read as zeros.                                                                                                                                                                          |

| 10    | N/U        | Not used. Read as one.                                                                                                                                                                            |

| 9, 8  | N/U        | Not used. Read as zeros.                                                                                                                                                                          |

| 7     | START      | <b>Start operation.</b> Setting this bit to a one will initiate the DMA controller and set the Active bit in the CSR. A pending start can only be reset by a software abort being set in the CCR. |

| 6,5   | N/U        | Not used. Read as zero.                                                                                                                                                                           |

| 4     | SOFT ABORT | Software Abort. Setting this bit stops a DMA transfer.                                                                                                                                            |

3

INT ENA

Interrupt Enable. This bit must be set to zero. The 2917

Bus Interrupter is used for DONE interrupts.

2-0

N/U

Not used. Read as zeros.

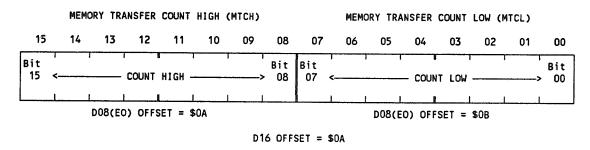

# Memory Transfer Count Register

The Memory Transfer Count (MTC) Register is a 16-bit counter which counts the number of words transferred by the DMA controller. A register layout of the Memory Transfer Count Register is given below:

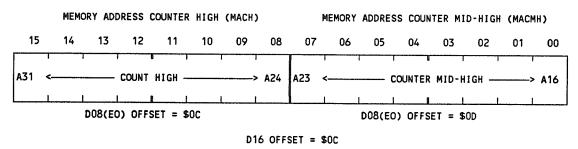

# Memory Address Counter Register

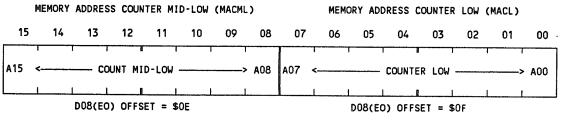

The Memory Address Counter Register is a 32-bit register which programs the starting address of a DMA transfer. Only the least significant 24-bits of the counter are implemented in the DMA controller. If 32 operations are desired, the upper eight address bits can be programmed in the 2917 Address Modifier Register. Two 16-bit Memory Address Counters must be loaded before the start of a DMA transfer. A register layout of the Memory Address Counter Register is given below:

# Memory Address Counter High (MACHI)

# Memory Address Counter Low (MACLO)

D16 OFFSET = \$0E

#### **BUS INTERRUPT REGISTERS**

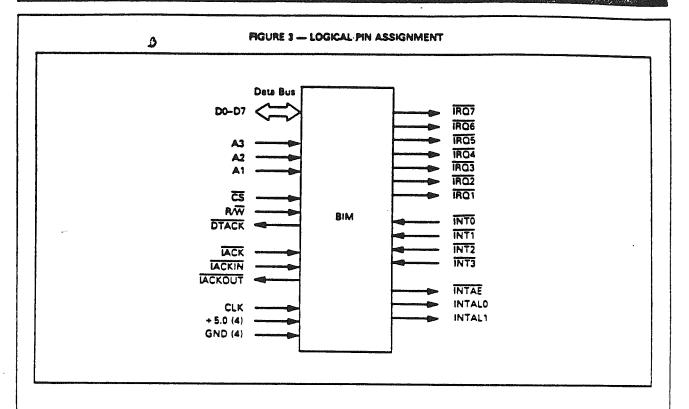

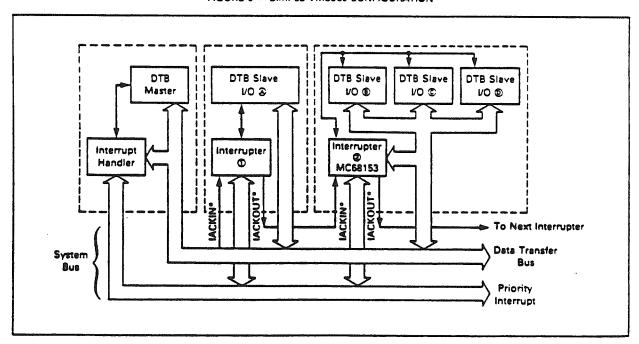

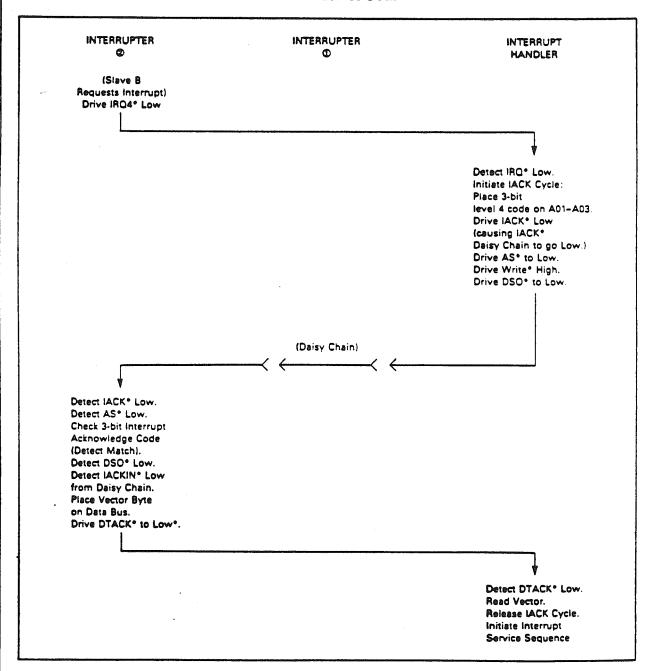

The Model 2917 uses the MC68153 Bus Interrupter to generate four separate interrupts. The four conditions that can cause an interrupt are: 1) a LAM, 2) DONE bit in the CSR set, 3) DMA Buffer Empty and 4) List Abort condition. If any two or more interrupts are set to the same interrupt request level, MC68153 gives preference to the highest number requester; that is, List Abort has the highest priority and LAM has the lowest. Programming information on the Bus Interrupter can be found below in the register descriptions and also in the Technical Specifications included in APPENDIX B of this manual.

### **Interrupt Control Registers**

The Interrupt Control Registers are used to enable and select the interrupt request level. A register layout and description of the Interrupt Control register is given below:

| 15   | 08       | 07          | 06                  | 05          | 04         | 03                 | 02                | 01                | 00                |

|------|----------|-------------|---------------------|-------------|------------|--------------------|-------------------|-------------------|-------------------|

| < No | ot Used> | FLAG<br>BIT | FLG<br>AUTO-<br>CLR | VEC-<br>TOR | INT<br>ENA | INT<br>AUTO<br>CLR | IRQ<br>LEVEL<br>2 | IRQ<br>LEVEL<br>1 | IRQ<br>LEVEL<br>O |

# Interrupt Control Register OFFSET

| LAM              | D16 = \$40 | D08(EO) = \$41 |

|------------------|------------|----------------|

| DONE             | D16 = \$42 | D08(EO) = \$43 |

| DMA BUFFER EMPTY | D16 = \$44 | D08(EO) = \$45 |

| LIST ABORT       | D16 = \$46 | D08(EO) = \$47 |

|                  |            |                |

| LIST ABORT | D16 :        | = \$46 D08(EO) = \$47                                                                                               |

|------------|--------------|---------------------------------------------------------------------------------------------------------------------|

| BIT#       | MNEMONIC     | DESCRIPTION                                                                                                         |

| 15-8       | N/U          | Not used. These bits are shown only for clarity when D16 operations are preformed. These bits are read as ones.     |

| 7          | FLAG         | <b>FLAG.</b> This bit can be used by software in conjunction with test and set instructions.                        |

| 6          | FLG AUTO-CLR | Flag Auto-Clear. When this bit is set, the FLAG bit is automatically cleared during an interrupt acknowledge cycle. |

| 5          | VECTOR       | Vector. This bit must be set to zero, the 2917 uses internal vectors.                                               |

| 4          | INT ENA      | Interrupt Enable. Setting this bit to a one will enable interrupts.                                                 |

| 3          | INT AUTO-CLR | Interrupt Auto-Clear. Setting this bit to a one will clear bit #4 (INT ENA) during an interrupt acknowledge cycle   |

responding to this request. To re-enable, bit #4 must be written with a one.

2-0

IRQ LEVEL

Interrupt Request Level. This three bit field determines the interrupt level, one through seven, to be generated. A value of zero disables the interrupt.

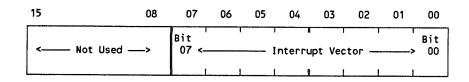

# **Interrupt Vector Registers**

Each Interrupt Control Register has its own associated Interrupt Vector Register. Each register is 8-bits wide and supplies a data byte during an interrupt acknowledge cycle. A register layout of the Interrupt Vector Register is given below:

OFFSET

| ZIZICII UDI V COTOI ITCEISTOI | OITOLI     |                |

|-------------------------------|------------|----------------|

|                               |            |                |

| LAM                           | D16 = \$48 | D08(EO) = \$49 |

| DONE                          | D16 = \$4A | D08(EO) = \$4B |

| DMA BUFFER EMPTY              | D16 = 4C   | D08(EO) = \$4D |

| LIST ABORT                    | D16 = \$4E | D08(EO) = \$4F |

### 2917 ON-BOARD REGISTERS

Interrupt Vector Register

All on-board registers are 16-bit wide. Only D16 word transfers to or from these are allowed. These eight registers are described in the following sections.

# Address Modifier Register

The Address Modifier Register (AMR) is a write only register. Information written into the AMR is used to drive the VMEbus Address Modifier signals and the upper eight address signals (A31-A24) when the 2917 transfers data as a VMEbus master. The upper eight address signals cannot increment during a DMA transfer. This is only an 8-bit latch register that is enabled when the 2917 becomes a VMEbus master. A register layout and a description of the AMR is given below:

#### ADDRESS MODIFIER REGISTER 15 14 13 12 11 10 09 80 07 06 05 04 03 02 01 00 A25 A31 A30 A29 A28 A27 A26 A24 N/U AM5 AM4 AM3 AM2 LWD AM1 OMA

D16 OFFSET = \$60

| BIT# | MNEMONIC | DESCRIPTION                                                                                                                                                                         |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-8 | A31-A24  | VME Address Lines. These added address bits are to make use of the full VME address range when the 2917 becomes a VMEbus master. These bits do not increment during a DMA transfer. |

| 7    | N/U      | Not used. Read as a one.                                                                                                                                                            |

| 6    | LWD      | <b>Longword.</b> This bit must be written to a one because the 2917 is unable to transfer 32-bit data words.                                                                        |

| 5-0  | AM5-AM0  | Address Modifier Codes. These bits must be written with the proper AM Code before a DMA transfer is started.                                                                        |

### **Command Memory Register**

The 2917 Command Memory is an 8K x 16-bit RAM memory. All CAMAC commands are executed from this memory. Data for one or more command lists is written or read as if the memory was a single register. The Memory Address is incremented automatically after each write or read operation. If multiple lists are present, the list to be executed is selected by first setting the Command Memory Address to that list. All lists must be CAMAC "Read" or "Write", with the following exceptions:

- 1. Read or write lists can contain dataless CAMAC commands, using Function Codes F(8) through F(15) and F(24) through F(31).

- 2. Read lists can contain Inline Write operations.

The instructions for the Command List (written as MEM DATA) can be selected from the following:

|    | Si | ngle | CAM               | IAC 7                  | [rans                       | sfer -                            | - Rea                                   | d, Wı                                         | rite, o                                            | r Cor                                                     | itrol                                                                 |                                           |                                                                                            |                                                                                      |                                                                                            |

|----|----|------|-------------------|------------------------|-----------------------------|-----------------------------------|-----------------------------------------|-----------------------------------------------|----------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 15 | 14 | 13   | 12                | 11                     | 10                          | 09                                | 08                                      | 07                                            | 06                                                 | 05                                                        | 04                                                                    | 03                                        | 02                                                                                         | 01                                                                                   | 00                                                                                         |

| 0  | 0  | 0    | 0                 | n                      | C4                          | r2                                | C1                                      | СМ                                            | TM2                                                | TM1                                                       | QM2                                                                   | QM1                                       | ues                                                                                        | uci                                                                                  | AD                                                                                         |

|    | ,  |      |                   |                        |                             |                                   |                                         | 0                                             | 0                                                  | 0                                                         | 0                                                                     | 0                                         | #32                                                                                        | WSI                                                                                  | AU                                                                                         |

|    |    |      |                   | I                      |                             |                                   |                                         | <u> </u>                                      |                                                    |                                                           |                                                                       |                                           |                                                                                            |                                                                                      |                                                                                            |

| 0  | 0  | N16  | N8                | N4                     | N2                          | N1                                | A8                                      | Α4                                            | A2                                                 | A1                                                        | F16                                                                   | F8                                        | F4                                                                                         | F2                                                                                   | F1                                                                                         |

|    | 0  | 0 0  | 15 14 13<br>0 0 0 | 15 14 13 12<br>0 0 0 0 | 15 14 13 12 11<br>0 0 0 0 0 | 15 14 13 12 11 10<br>0 0 0 0 0 C4 | 15 14 13 12 11 10 09<br>0 0 0 0 0 c4 c2 | 15 14 13 12 11 10 09 08<br>0 0 0 0 0 C4 C2 C1 | 15 14 13 12 11 10 09 08 07 0 0 0 0 0 C4 C2 C1 CM 0 | 15 14 13 12 11 10 09 08 07 06 0 0 0 0 C4 C2 C1 CM TM2 0 0 | 15 14 13 12 11 10 09 08 07 06 05  0 0 0 0 0 C4 C2 C1 CM TM2 TM1 0 0 0 | 0 0 0 0 0 C4 C2 C1 CM TM2 TM1 QM2 0 0 0 0 | 15 14 13 12 11 10 09 08 07 06 05 04 03  0 0 0 0 0 C4 C2 C1 CM TM2 TM1 QM2 QM1  0 0 0 0 0 0 | 15 14 13 12 11 10 09 08 07 06 05 04 03 02  0 0 0 0 0 C4 C2 C1 CM TM2 TM1 QM2 QM1 WS2 | 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 0 0 0 0 0 C4 C2 C1 CM TM2 TM1 QM2 QM1 WS2 WS1 |

D16 OFFSET = \$62

W(2)

0

0

A12

A11

A10

A9

| Model | 2011              | * <i>L</i> J | L          |        |        |                 |              |            |                              |              |        |          |          |       |     |       |

|-------|-------------------|--------------|------------|--------|--------|-----------------|--------------|------------|------------------------------|--------------|--------|----------|----------|-------|-----|-------|

| (b)   |                   | Si           | ingle      | CAN    | IAC '  | Tran            | sfer -       | – Inli     | ne W                         | rite (       | usual  | ly in    | Read     | list) |     |       |

|       | 15                | 14           | 13         | 12     | 11     | 10              | 09           | 08         | 07                           | 06           | 05     | 04       | 03       | 02    | 01  | 00    |

| ₩(1)  | 0                 | 0            | 0          | 0      | 0      | C4              | C2           | C1         | CM<br>O                      | TM2          | TM1    | QM2<br>0 | QM1<br>0 | ₩S2   | WS1 | AD    |

| ₩(2)  | 0                 | 0            | N16        | N8     | N4     | N2              | N1           | A8         | A4                           | A2           | A1     | F16      | F8       | F4    | F2  | F1    |

| ₩(3)  | W16               | W15          | <b>W14</b> | W13    | W12    | w11             | w10          | W9         | ₩8                           | W7           | ₩6     | ₩5       | W4       | W3    | W1  | AD    |

| ₩(4)  | х                 | х            | х          | х      | х      | х               | х            | х          | W24                          | W23          | W22    | W21      | ₩20      | W19   | ₩18 | W17   |

|       | ,                 | Note:        | ⊌ord #     | 4 is a | dummy  | word            | for 16       | -bit I     | nline I                      | Write        | operat | ion.     | <b>B</b> |       |     | ····· |

|       | D16 OFFSET = \$62 |              |            |        |        |                 |              |            |                              |              |        |          |          |       |     |       |

| (c)   |                   | Bl           | ock (      | CAM    | AC T   | rans            | fer          |            |                              |              |        |          |          |       |     |       |

| ſ     | 15                | 14           | 13         | 12     | 11     | 10              | 09           | 80         | 07                           | 06           | 05     | 04       | 03       | 02    | 01  | 00    |

| W(1)  | 0                 | 0            | 0          | 0      | 0      | C4              | C2           | C1         | CM<br>0                      | TM2<br>0     | TM1    | QM2<br>X | QM1<br>X | WS2   | WS1 | AD    |

| W(2)  | 0                 | 0            | N16        | N8     | N4     | N2              | N1           | <b>A</b> 8 | A4                           | A2           | A1     | F16      | F8       | F4    | F2  | F1    |

| W(3)  |                   |              | (          | The 2  | s Comp | olement<br>trar | of th        | ne numb    | JNT LOW<br>Der of<br>Dr from | 16-bi        |        | word 1   | o be     |       |     |       |

| ¥(4)  |                   | 7.0          |            |        | ( A c  | dummy r         | WC<br>egiste | ORD COL    | JNT HIG<br>Jally s           | iH<br>set to | all or | nes.)    |          |       |     |       |

| (d)   |                   | JU           | JMP i      | instr  | uctio  | n – .           |              |            | T = \$6                      |              | mand   | l list.  |          |       |     |       |

| ٦     | 15                | 14           | 13         | 12     | 11     | 10              | 09           | 08         | 07                           | 06           | 05     | 04       | 03       | 02    | 01  | 00    |

| ₩(1)  | 0                 | 0            | 0          | 0      | 0      | 0               | 0            | 0          | CM                           | TM2          | TM1    | 0        | 0        | 0     | 0   | 0     |

D16 OFFSET = \$62

Α7

A6

A5

Α4

А3

A2

A1

ΑO

**8**A

| (e)  |    | HA | ALT i | instr | uctio | n – I | End o | f Con | nman | d list |     |    |    |    |    |    |

|------|----|----|-------|-------|-------|-------|-------|-------|------|--------|-----|----|----|----|----|----|

|      | 15 | 14 | 13    | 12    | 11    | 10    | 09    | 08    | 07   | 06     | 05  | 04 | 03 | 02 | 01 | 00 |

| W(1) | 0  | 0  |       |       |       | 0     | 0     | 0     | CM   | TM2    | TM1 | 0  | 0  | 0  | 0  |    |

| W(I) | ١  | U  | U     | U     | U     | U     | U     | U     | 1    | 0      | 0   | U  | U  | U  | U  | Ů  |

D16 OFFSET = \$62

Any list can contain a combination of the above instructions, terminated by the HALT instruction.

The Mode word (word #1) in the list instructions is partitioned as follows:

|       | , , , , , , , , , , , , , , , , , , , , |                                                                                                                                |

|-------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| BIT#  | MNEMONIC                                | DESCRIPTION                                                                                                                    |

| 15-11 | N/U                                     | Not Used. Don't care.                                                                                                          |

| 10-8  | C4,C2,C1                                | <b>Crate.</b> This 3-bit field selects one of eight 3922 Crate Controllers.                                                    |

| 7     | CM                                      | Command Mode: 0 = CAMAC transfer 1 = Non-CAMAC instruction. (HALT, etc.)                                                       |

| 6,5   | TM2,TM1                                 | Transfer Mode: CM = 0 0 0 = Single CAMAC transfer 0 1 = Block CAMAC transfer 1 0 = Not Used 1 1 = Single Inline write transfer |

|       |                                         | Transfer Mode: CM = 1 0 0 = HALT instruction 0 1 = Not Used 1 0 = JUMP instruction 1 1 = Not Used                              |

| 4,3   | QM2,QM1                                 | Q-Mode Transfer Type: 0 0 = Q-Stop, Single, Inline Write 0 1 = Q-Ignore 1 0 = Q-Repeat 1 1 = Q-Scan                            |

| 2,1   | WS2,WS1                                 | Word Size:                                                                                                                     |

0.0 = 24-bit CAMAC transfer

0 1 = 16-bit CAMAC transfer

1.0 = Not Used

1.1 = Not Used

0 AD

**Abort Disable.** Data of zero will Abort a transfer on an error (refer to the Operation Section of this manual for a description of error for each mode). Data of one disables Abort.

# Command Memory Address Register

The Command Memory Address (CMA) Register is a 16-bit Write/Read Counter. When loading a new list, this register is loaded with an address that points to the initial word location for that command list. When writing or reading the Command Memory, the address register is auto-incremented after each read or write operation. After a HALT instruction is encountered or the list is aborted, the Command Memory Address Register points to the next list address. A layout of the Command Memory Address Register is given below:

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 80    | 07    | 06     | 05      | 04    | 03 | 02 | 01 | 00 |

|----|----|----|----|----|----|----|-------|-------|--------|---------|-------|----|----|----|----|

| 0  | 0  | 0  | <  |    |    |    | —— Сс | mmand | Memory | / Addre | ess — |    |    |    | -> |

D16 OFFSET = \$64

# Command Word Count Register

The Command Word Count (CWC) Register is a 16-bit read-only counter which contains the 2's complement of the number of words not yet executed in a CAMAC block transfer read or write operation. When a CAMAC block transfer is executed, this register is loaded by the Command Memory Sequencer with the initial word count from the command list and incremented as transfers occur for that block. When a block transfer is aborted, the "current" word count can be determined by reading this register. Note that the data in this register monitors the last block operation executed not the total word count for all the list operations. A register layout for the Command Word Count Register is given below:

D16 OFFSET = \$66

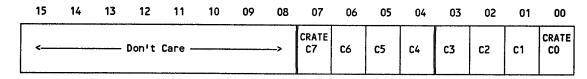

# Service Request Register

The Service Request Register (SRR) provides information regarding LAMs in a multicrate system. When this register is read, the 2917 issues a Parallel Poll to all 3922s connected to the bus.

The 8-bits represent the eight possible crate addresses. A true bit (1) in the SRR indicates that its associated crate is asserting its LAM line. If any 3922 is requesting service, the LAM signal (bit #9 of the CSR) is set. A register layout of the Service Request Register is given below:

D16 OFFSET = \$68

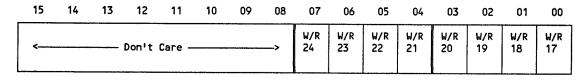

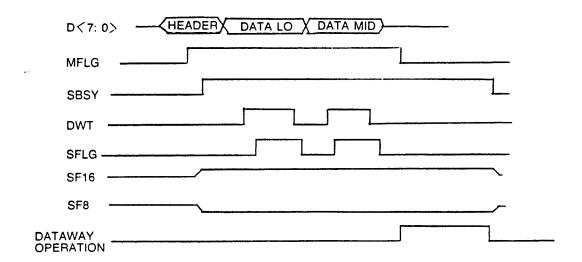

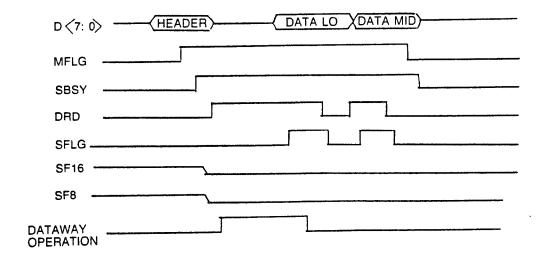

### **Data Low Register**

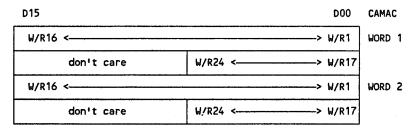

The Data Low Register (DLR) is used to access the lower 16-bits of the 24-bit CAMAC word. During a CAMAC write operation, F(16)-F(23), the contents of the DLR are used to generate the data signals on the CAMAC write data lines W16 through W1. During CAMAC read operations, F(0)-F(7), the DLR is loaded with the data signals present on the CAMAC read data lines R16 through R1. A register description of the Data Low Register is given below:

| <br>15 | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| W/R    | ₩/R | W/R | ₩/R | ₩/R | ⊌/R | ₩/R | ⊌/R | W/R | ₩/R | W/R | ₩/R | ₩/R | W/R | ₩/R | ⊌/R |

| 16     | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   |

D16 OFFSET = \$6A

#### Data High Register

The Data High Register (DHR) is used to access the upper 8-bits of the 24-bit CAMAC word. During a CAMAC write operation, F(16)-F(23), the contents of the DHR are used to generate the data signals on the CAMAC write data lines W24 through W17. During CAMAC read operations, F(0)-F(7), the DHR is loaded with the data signals present on the CAMAC read data lines R24 through R17. A register description of the Data Low Register is given below:

D16 OFFSET = \$6C

### Control Status Register

The Control Status Register (CSR) is used to start the 2917 operations and monitor the results of those operations. A layout and description of the Control Status Register is given below:

| _ | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07   | 06  | 05  | 04  | 03  | 02   | 01   | 00 |

|---|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|------|------|----|

|   | ERR | ABT | TMO | RST | TM2 | TM1 | LAM | RDY | DONE | DMA | DIR | ID2 | ID1 | NO-X | NO-Q | GO |

D16 OFFSET = \$6E

| BIT#  | MNEMONIC | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                  |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|