# INTRODUCTION

The V122 PCI FOXI Highway Driver (IHD) is a full size PCI card, which interfaces the PCI bus to the Interconnect Highway. The Interconnect Highway is a fiber-optic highway, which allows serial access to up to 126 slave nodes. These slave nodes may be any combination of CAMAC Crate Controllers, VXI Chassis Controllers and VME Chassis Controllers. The maximum signaling distance between fiber-optic nodes is 2 kilometers. The highway runs at 125 Megabits-per-second using 12-bits per word, 8 of which are information bits and 4 of control. Therefore, the maximum bandwith of data transfers on the highway is 10 Megabytes-per-second.

The V122 executes highway operations provided by a list of instructions preloaded into a 32K x 32-list memory. This memory is loaded prior to initiating operations by programmed I/O transfers. Once list processing is initiated, data transfers to/from the V122 may occur using either DMA or programmed transfers. DMA operations to/from the V122 are executed using a 32-bit word format.

The list may contain such instructions as Single Operations, Block Transfer Operations, Single Inline Write Operations, Generate Host Interrupts, Load Loop Counter, and Conditional/Unconditional Branches. These instructions allow for a very versatile list. The format of the instruction varies depending on the type of slave node being accessed.

A Demand FIFO is provided to retain up to 2048 demand messages. These messages are generated by VXI/VME slaves. VXI/VME slaves generate these messages in response to interrupt requests in the chassis. When these messages are received by the V122, the chassis address and a demand identification byte are stored in the FIFO. Optionally, the receipt of a demand message may assert an interrupt request to the PCI bus.

## INSTALLATION

The Model V122 is designed to fit into any full size PCI expansion slot. After selecting the desired Highway Timeout value, the V122 is ready to be installed in the computer.

Before the installation is initiated, turn off the power to the computer and remove the power cord. Remove the cover to the computer and locate an empty expansion slot. Remove the blank plate from the mounting rail of the selected slot. Insert the V122 into the slot and secure the mounting plate with the screw that was removed from the blank plate. Replace the cover on the computer and then plug the power cord back into the unit.

After the card is installed in the computer, connect the fiber optic cables to the V122. The top fiber optic connector on the V122 is the highway output connector. The bottom fiber optic connector is the highway input connector. One fiber optic cable should run from the V122 highway output connector (top) to the first chassis V160 Slot0 input connector (for VXI). A second fiber optic cable should run from the bottom highway input fiber optic connector on the V122 to the highway output connector on the V160.

## **HIGHWAY TIMEOUT SELECTION**

The V122 contains a strap selectable timer to control the timeout value for the highway. If the V122 transmits a message on the highway and does not receive a reply message within the selected timeout period, an error is generated and the highway is reset. This timeout value ranges from 3 seconds to 10 seconds. The timeout may also be disabled to allow for an infinite timeout value. Please refer to Appendix B of this manual for the location and settings of the Highway Timeout.

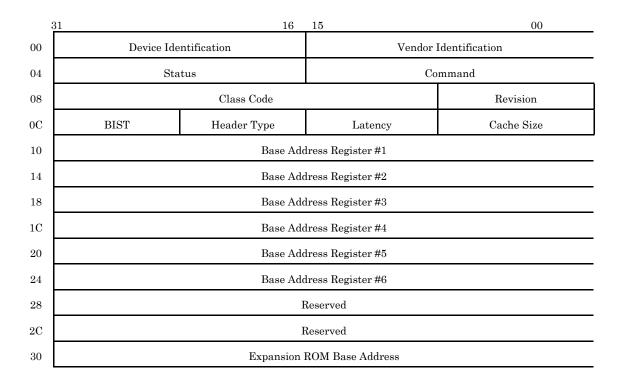

# PCI CONFIGURATION SPACE

The PCI Specification mandates a 64-byte Configuration Header that describes the requirements of add-in cards. The data contained in this region uniquely identifies the device and allows for generic control of the device. The configuration data indicates the memory requirements of the device along with other device specific information.

This section describes the 64 bytes of configuration space implemented by the V122. The following diagram is a composite chart showing the configuration header.

| 34 |                 | Η               | Reserved      |                |  |  |  |  |  |  |  |  |  |

|----|-----------------|-----------------|---------------|----------------|--|--|--|--|--|--|--|--|--|

| 38 | Reserved        |                 |               |                |  |  |  |  |  |  |  |  |  |

| 3C | Maximum Latency | Minimum Latency | Interrupt Pin | Interrupt Line |  |  |  |  |  |  |  |  |  |

## **VENDOR IDENTIFICATION Field**

The VENDOR IDENTIFICATION field contains read-only bits that identify the manufacturer of the device. The ID assigned to KineticSystems is 11F4 Hex.

## **DEVICE IDENTIFICATION Field**

The DEVICE IDENTIFICATION field contains read-only bits, which identify a particular device. The DEVICE ID field for this unit is 0112 Hex.

## PCI COMMAND Register

The COMMAND field contains write/read bits used to configure basic PCI functions. The following diagram shows the COMMAND field as implemented by the V122.

| 15 | 14 | 13 | 12 | 11 | 10 | 09                 | 08                 | 07 | 06                 | 05 | 04 | 03 | 02                 | 01                 | 00                 |

|----|----|----|----|----|----|--------------------|--------------------|----|--------------------|----|----|----|--------------------|--------------------|--------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | FS<br>T<br>BT<br>B | SE<br>R<br>EN<br>A | 0  | PE<br>R<br>EN<br>A | 0  | 0  | 0  | MA<br>S<br>EN<br>A | ME<br>M<br>EN<br>A | I/<br>O<br>EN<br>A |

<sup>&</sup>lt;15:10> Not Used. These bits are not used and read as zeros.

- <9> FAST BACK-TO-BACK is a write/read bit used to enable or disable the V122 from executing "fast" back-to-back bus master cycles after completing a write cycle. Setting this bit to a one enables fast transfers and a zero disables the mode.

- <8> SYSTEM ERROR ENABLE is a write/read bit used to enable and disable the V122 from driving the PCI SYSTEM ERROR (SERR) signal. This signal is used by the V122 to inform the host CPU of a parity error during an address or control portion of a bus operation. Setting this bit to a one enables the V122 to assert SERR and disabled with a zero.

- <7> Not Used. These bits are not used and read as zeros.

- <6> PARITY ERROR ENABLE is a write/read bit used to enable and disable the V122 from driving the PCI PARITY ERROR (PERR) signal. This signal is

asserted by the V122 when a parity error is detected during a data transfer to/from the V122. The PERR function is enabled by setting this bit to a one and disabled with a zero.

- <5:3> Not Used. These bits are not used and read as zeros.

- <2> BUS MASTER ENABLE is a write/read bit which enables and disables the V122 from executing bus master operations. Setting this bit to a one enables the V122 to function as a bus master and a zero disables the master operation. Since the V122 interface hardware actually controls bus master operations, this bit is not used.

- <1> MEMORY SPACE ENABLE is a write/read bit that allows the V122 to function in memory regions that may be defined in one of the base address registers. Since the V122 is initially configured as an I/O device, this bit should be set to zero.

- <0> I/O SPACE ENABLE is a write/read bit that allows the V122 to function in I/O regions as defined in one of the base address registers. This bit is set to a one that allows the V122 to function in I/O regions.

## **PCI STATUS Register**

The PCI STATUS Register is used to record status information regarding PCI bus transfers. This register contains read-only bits and write/read bits. The following diagram shows the Status Register bits implemented by the V122.

| 15         | 14         | 13         | 12         | 11         | 10         | 09         | 08        | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|------------|------------|------------|------------|------------|------------|------------|-----------|----|----|----|----|----|----|----|----|

| PAR<br>DET | SIG<br>SER | RCV<br>MAB | RCV<br>TAB | SIG<br>TAB | DEV<br>TM1 | DEV<br>TM0 | DP<br>RPT | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

- <15> DETECTED PARITY ERROR is a write/read bit that is set whenever the V122 detects a PCI parity error. This bit does not depend on the state of the PAR ENA bit in the PCI COMMAND Register. Once an error has been detected, this may be cleared by writing a one to bit position 15.

- <14> SIGNALED SYSTEM ERROR is a write/read bit which is set whenever the V122 asserts the PCI SYSTEM ERROR (SERR) signal. Once this bit is set, it may be cleared by writing a one to bit position 14.

- <13> RECEIVED MASTER ABORT is a write/read bit that is set when the V122 is accessed as a target and the master aborts the transaction. This bit can be reset by writing a one to this bit position.

| <12>   | RECEIVED TARGET ABORT is a write/read bit that is set when the V122, acting as a bus master, has initiated a transfer and the addressed target aborts the transfer. This bit can be reset by writing a one to this bit position.                                                                              |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <11>   | SIGNALED TARGET ABORT is a write/read bit that is set when a bus master accesses the V122 as a target and the V122 aborts the cycle. This bit is reset when a one is written to this bit location.                                                                                                            |

| <10:9> | DEVICE SELECT TIMING 1 and 0 encode the timing of the PCI DEVSEL (Device Select) signal. This time reflects the slowest time that a device asserts DEVSEL for any bus command except Configuration Read and Configuration Write. Since the V122 may be accesses in the fast mode, these bits are set to zero. |

| <8>    | DATA PARITY REPORTED is a write/read bit that is set when the V122 detects<br>a parity error when the V122 is a bus master. This bit can be reset by writing a<br>one to this bit position.                                                                                                                   |

## **REVISION Field**

The REVISION field contains read-only bits that reflect the current revision level of the V122. The V122 starts at revision one and subsequent revisions increment the number.

## **CLASS CODE Field**

The CLASS CODE field actually contains three subfields that represent device characteristics. These three subfields are the BASE CLASS, the SUB-CLASS and the PROG I/F fields. These subfields define such parameters as network controllers, display controllers, video device, etc. The V122 does not fit into any of the defined class codes. Therefore, the class code that the V122 uses is FF0000 Hex that indicates that the V122 class code is undefined by the PCI specification.

## CACHE LINE SIZE Field

The CACHE LINE SIZE field is used by the system to define the cache line size. The V122 does not use Memory Write and Invalidate PCI bus cycles when operating as a bus master and therefore sets this field to zero.

## LATENCY TIMER REGISTER

The LATENCY TIMER REGISTER is only used when the V122 is operating as a bus master. The values loaded in this register are the minimum number of PCI bus clocks that the V122 can be guaranteed as a master. After the V122 becomes bus master and asserts the PCI FRAME signal, the Latency Timer is decremented for each PCI bus clock. Subsequent to the timer decrementing to zero, the V122 ignores the PCI bus grant signal and continues to

transfer data until the timer expires. The value loaded into this register is in multiples of eight clock cycles since the low 3 bits of this field are hardwired to zero.

## HEADER Field

The HEADER field establishes whether a PCI device contains a single function or multifunction PCI bus agent. Since the V122 contains only a single function, this field is set to zero.

## **BUILD IN SELF TEST Field**

This field is used to present Built In Self-Test diagnostic results to a bus master. The V122 does not implement BIST and returns a zero for this field.

## BASE ADDRESS REGISTERS

The BASE ADDRESS REGISTERS are used to specify the memory or I/O requirements of addin devices and also to configure the base addresses of these devices.

After power-up, system software can determine how much address space a particular device requires by writing all ones to a base address register and then reading that value back. The device returns zeros in all address bit locations that do not define the base address.

The least significant bit in each of the base address registers is used for specifying the region of address space for which the device is to reside. A value of zero specifies a memory region and a value of one specifies an I/O region. The V122 is configured to operate in the I/O region.

The V122 implements two of the Base Address registers. The first Base Address register is used to communicate with the PCI Interface Operational Registers (IOR) and the second is used to communicate with the Highway Operational Registers (HOR). The Interface Operational Registers require 16 longwords (64 bytes) of address space. A read of the first base address register, after a write of all ones, returns the value FFFFFC1 Hex, indicating a request for 16 longwords of I/O space.

The Highway Operational Registers require 16 longwords (64 bytes) of address space. A read of the second base address register, after a write of all ones, returns the value FFFFFC1 Hex, indicating a request for 16 longwords in I/O space.

After the system software has determined the total address space requirements of the system, it assigns the base addresses to memory and I/O devices by writing their Base Address Registers.

## EXPANSION ROM BASE ADDRESS Register

This field is used to assign a physical memory address to expansion ROM in a system. The V122 does not contain an expansion ROM and therefore does not require use of this field.

## **INTERRUPT LINE Field**

This write/read field is used for communicating interrupt routing information and is configured by the PCI BIOS after power-up. The value in this field informs the system interrupt controller which pin of the controller the interrupt is connected to.

## **INTERRUPT PIN Field**

The INTERRUPT PIN field is read-only and specifies which PCI interrupt pin that the V122 is connected to. The V122 returns a value of one in this field indicating that it uses the INTA interrupt.

#### MINIMUM GRANT Register

This write/read register is used by bus masters to specify the minimum amount of time the device needs for a period of burst transfers. Since the V122 does not have this requirement, a value of zero must be used.

## V122 Operational Registers

The V122 PCI FOXI Highway Driver uses several I/O addressable registers to control and monitor operations. All data transfers to/from the V122 must be executed using 32-bit data transfers. The V122 does not accommodate byte or shortword accesses.

The V122 incorporates a PCI Interface Controller manufactured by Applied Micro Circuits Corporation, the S5933. This device contains several PCI configuration registers and also some of the V122 operational registers. The primary register that the V122 uses is the bi-directional FIFO register. This FIFO is used in transferring data to/from slave nodes on the interconnect highway. A Control/Status register provides access to FIFO flags.

## **PCI Interface Operational Registers**

The PCI Interface Operational Registers are contained in the PCI interface chip used on the V122. This chip is the S5933 and is manufactured by Applied Micro Circuits Corporation. The base address of these registers is loaded by power-on BIOS routines and is contained in the Base Address Register #1 location of the PCI Configuration Registers.

Note: All references to Incoming and Outgoing are referred to the host. An Outgoing operation is a write operation from the host and an Incoming operation is a read operation from the V122.

The following chart shows the various PCI Interface Registers along with their offsets from the base address.

| <u>Offset</u> | Register                    | Access       |

|---------------|-----------------------------|--------------|

| 0             | Outgoing Mailbox #1         | W/R          |

| 4             | Outgoing Mailbox #2         | W/R          |

| 8             | Outgoing Mailbox #3         | W/R          |

| $\mathbf{C}$  | Outgoing Mailbox #4         | W/R          |

| 10            | Incoming Mailbox #1         | R            |

| 14            | Incoming Mailbox #2         | R            |

| 18            | Incoming Mailbox #3         | R            |

| $1\mathrm{C}$ | Incoming Mailbox #4         | R            |

| 20            | Data FIFO                   | W/R          |

| 24            | Master Write Address        | R            |

| 28            | Master Write Transfer Count | R            |

| $2\mathrm{C}$ | Master Read Address         | $\mathbf{R}$ |

| 30            | Master Read Transfer Count  | $\mathbf{R}$ |

| 34            | Mailbox Empty/Full Status   | W/R          |

| 38            | Interrupt Control/Status    | W/R          |

| 3C            | Bus Master Control/Status   | W/R          |

## **Outgoing/Incoming Mailboxes**

The Incoming and Outgoing Mailboxes are used by the KineticSystems software drivers to provide a communication mechanism between the list processor and the host CPU. The details of this communication scheme is beyond the scope of this manual.

## **Data FIFO Register**

The Data FIFO Register is composed of two 8 x 32-bit FIFOs located in the PCI interface chip. When executing Interconnect Highway operations, all write and read data passes through these FIFOs. Data transfers to or from these FIFOs can be done by either programmed transfers executed by the host or by allowing the V122 to become a bus master and transfer the data.

When executing write operations to the highway, the write data is first written to the Data FIFO Register. The data is then moved from the PCI interface chip to a 2K X 16-bit FIFO external to the chip in preparation for transmission onto the highway. When read operations from the highway are executed, the read data is initially stored in a 2K X 16 FIFO before transfer to the PCI interface chips' 8 X 32 FIFO.

Several status indicators are provided which indicate the amount of data contained in the PCI interface chip FIFOs and the external 2K X 32 FIFOs. The Bus Master Control/Status register contains 6 status bits that correspond to the PCI Interface chip internal FIFOs. Two status bits are provided in the Control/Status register of the Highway Operational registers for the

two external 2K X 32 FIFOs. Both sets of status flags must be used in determining the amount of data contained in the write FIFO data path or the read FIFO data path.

## Master Write Address Register

The Master Write Address Register is a read-only register that contains the last address that was accessed during a bus master write operation executed by the V122. This address is actually pointing to one longword beyond the last address accessed since the memory address is incremented after each execution of a data transfer.

The Master Write Address Register can be written to by either the DSP or by programmed I/O through the Highway Operational Registers. When the Memory Address Register (MAR) of the Highway Operational Registers is written by programmed I/O or by the DSP, a hardware mechanism loads both the Master Write Address Register and the Master Read Address Register.

After a bus master operation completes, the current memory address minus 4 may be read from the Master Write Address Register. The initial memory address used for the bus master operation can be read through the Memory Address Register of the Highway Operational Registers.

#### Master Write Transfer Count Register

This register is not used by the V122. When executing bus master operations, the V122 uses the Total Transfer Count Register of the Highway Operational Registers to determine the number of bus operations to perform.

## Master Read Address Register

The Master Read Address Register is a read-only register that contains the last address that was accessed during a bus master read operation executed by the V122. This address is actually pointing to one longword beyond the last address accessed since the memory address is incremented after each execution of a data transfer.

The Master Read Address Register can be written to by either the DSP or by programmed I/O through the Highway Operational Registers. When the Memory Address Register (MAR) of the Highway Operational Registers is written by programmed I/O or by the DSP, a hardware mechanism loads both the Master Write Address Register and the Master Read Address Register.

After a bus master operation completes, the current memory address minus 4 may be read from the Master Read Address Register. The initial memory address used for the bus master operation can be read through the Memory Address Register of the Highway Operational Registers.

# Master Read Transfer Count Register

This register is not used by the V122. When executing bus master operations, the V122 uses the Total Transfer Count Register of the Highway Operational Registers to determine the number of bus operations to perform.

## Mailbox Empty/Full Status Register

The Empty/Full Status Register is used by the KineticSystems software driver to implement "special" functions. The communication scheme for the mailbox register used in the software driver is beyond the scope of this manual. The following shows the bit pattern for the Mailbox Empty/Full Status Register. The register is shown here for completeness only.

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| IMB |

| 4D  | 4C  | 4B  | 4A  | 3D  | 3C  | 3B  | 3A  | 2D  | 2C  | 2B  | 2A  | 1D  | 1C  | 1B  | 1A  |

| 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |

| OMB |

| 4D  | 4C  | 4B  | 4A  | 3D  | 3C  | 3B  | 3A  | 2D  | 2C  | 2B  | 2A  | 1D  | 1C  | 1B  | 1A  |

The IMB bits refer to the incoming mailbox registers. The OMB bits refer to the outgoing mailbox registers. The numbers 1 through 4 refer to the mailbox number and the letters D through A refer to the byte within the longword. Since the mailbox may only be written as longwords from either side, all byte indicators within a word will be either set or cleared.

## PCI Interface Interrupt Control/Status Register

The PCI Interface Interrupt Control/Status Register of the PCI Interface Operational Registers is used to monitor and control interrupts generated by the PCI interface chip. Before an interrupt is sourced from the interface chip to the PCI bus, it must be enabled with the PCI INTERRUPT ENABLE bit in the Interrupt Control/Status Register of the Highway Operational Registers.

The following shows the bit pattern for the Interrupt Control/Status Register of the PCI Interface Operational Registers.

| <br>31    | 30        | 29 | 28        | 27         | 26         | 25         | 24         | 23         | 22 | 21         | 20         | 19         | 18         | 17         | 16         |

|-----------|-----------|----|-----------|------------|------------|------------|------------|------------|----|------------|------------|------------|------------|------------|------------|

| 0         | 0         | 0  | 0         | 0          | 0          | 0          | 0          | INT<br>REQ | 0  | TAR<br>ABT | MAS<br>ABT | RTC        | WTC        | IMB<br>SRC | OMB<br>SRC |

| 15        | 14        | 13 | 12        | 11         | 10         | 09         | 08         | 07         | 06 | 05         | 04         | 03         | 02         | 01         | 00         |

| RTC<br>IE | WTC<br>IE | 0  | IMB<br>IE | IMB<br>EMB | IMB<br>EMA | IMB<br>EBB | IMB<br>EBA | 0          | 0  | 0          | OMB<br>IE  | OMB<br>EMB | OMB<br>EMA | OMB<br>EBB | OMB<br>EBA |

<31:24> These 8 bits control endian conversion and must be set to zero for the V122 to operate properly.

<23> INTERRUPT REQUEST is a read-only bit that is set when the PCI interface chip is requesting service. This bit reflects the interrupt output of the PCI chip and does not indicate that the PCI bus interrupt is asserted. If the PCI Interrupt Enable bit of the Interrupt Control/Status Register of the Highway Operational Registers is set to a one, this bit indicates that a PCI bus interrupt is requested.

<22> This bit is not used and is read as a zero.

| <21> | TARGET ABORT is a read/write-to-clear bit that indicates when the V122 executes a bus master transfer and the addressed target aborts the transfer. An interrupt source is generated when this bit is set. This bit is cleared by writing a one to this bit position.                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <20> | MASTER ABORT is a read/write-to-clear bit that indicates when the V122 executes a bus master operation and the addressed target does not respond. An interrupt source is generated when this bit is set. A write operation to this register with this bit set to a one clears the bit.                                   |

| <19> | READ TRANSFER COMPLETE is a read/write-to-clear bit that is set when the Master Read Transfer Count Register is decremented to zero. Since the V122 does not use this register, the bit should never be set.                                                                                                             |

| <18> | WRITE TRANSFER COMPLETE is a read/write-to-clear bit that is set when the Master Write Transfer Count Register is decremented to zero. Since the V122 does not use this register, the bit should never be set.                                                                                                           |

| <17> | INCOMING MAILBOX INTERRUPT SOURCE is a read/write-to-clear bit that<br>is set to a one when the mailbox selected by bits 12 through 8 of this register are<br>written by the DSP. An interrupt source is generated when this bit is a one. A<br>write operation with this bit set to a one clears the bit.               |

| <16> | OUTGOING MAILBOX INTERRUPT SOURCE is a read/write-to-clear bit that<br>is set to a one when the mailbox selected by bits 4 through 0 of this register is<br>read by the DSP. An interrupt source is generated if this bit is set to a one. A<br>write operation with this bit set to a one causes the bit to be cleared. |

| <15> | READ TRANSFER COMPLETE INTERRUPT ENABLE is a write/read bit used<br>to enable and disable the generation of an interrupt when the read transfer<br>count is exhausted. Since the V122 does not used the Master Read Transfer<br>Count, this bit should always be set to the disable state.                               |

| <14> | WRITE TRANSFER COMPLETE INTERRUPT ENABLE is a write/read bit<br>used to enable and disable the generation of an interrupt when the write<br>transfer count is exhausted. Since the V122 does not use the Master Write<br>Transfer Count, this bit should always be set to the disable state.                             |

| <13> | This bit is not used and is read as a zero.                                                                                                                                                                                                                                                                              |

| <12> | INCOMING MAILBOX INTERRUPT ENABLE is a write/read bit that is used to<br>enable/disable the generation of an interrupt source when a preselected<br>incoming mailbox register is written. Bits 11 through 8 of this register select<br>which mailbox register write operation will generate the interrupt source.        |

- <11:10> INCOMING INTERRUPT SELECT bits are used to select which incoming mailbox write operations are to generate an interrupt source. The binary combinations of these bits determine which mailbox to enable. Data 0 is mailbox #1, data 1 is mailbox #2, data 2 is mailbox #3 and data 3 is mailbox #4.

- <9:8> INCOMING MAILBOX BYTE INTERRUPT SELECT bits are used to select which byte of the mailbox, selected by bits 11 and 10 of this register, are actually causing the interrupt source.

- <7:5> These bits are not used and are read as zeros.

- <4> OUTGOING MAILBOX INTERRUPT ENABLE is a write/read bit that is used to enable/disable the generation of an interrupt when a preselected outgoing mailbox register is written. Bits 3 through 0 of this register select which mailbox write operation will generate the interrupt source.

- <3:2> OUTGOING INTERRUPT SELECT bits are used to select which outgoing mailbox write operations are to generate an interrupt source. The binary combinations of these bits determine which mailbox to enable. Data 0 is mailbox #1, data 1 is mailbox #2, data 2 is mailbox #3 and data 3 is mailbox #4.

- <1:0> OUTGOING MAILBOX BYTE INTERRUPT SELECT bits are used to select which byte of the mailbox, selected by bits 3 and 2 of this register, are actually causing the interrupt source.

## **Bus Master Control/Status Register**

The Bus Master Control/Status Register is used to monitor/control bus master operations and to check status of the two PCI interface chip FIFOs. The following diagram shows the bit pattern for the Bus Master Control/Status Register.

| 31 | 30 | 29 | 28 | 27         | 26         | 25         | 24         | 23 | 22 | 21        | 20        | 19         | 18        | 17        | 16         |

|----|----|----|----|------------|------------|------------|------------|----|----|-----------|-----------|------------|-----------|-----------|------------|

| 0  | 0  | 0  | 0  | MBX<br>RST | INF<br>RST | OTF<br>RST | AON<br>RST | 0  | 0  | 0         | 0         | 0          | 0         | 0         | 0          |

| 15 | 14 | 13 | 12 | 11         | 10         | 09         | 08         | 07 | 06 | 05        | 04        | 03         | 02        | 01        | 00         |

| 0  | 0  | 0  | 0  | 0          | 0          | 0          | 0          | 0  | 0  | IFE<br>MT | IFI<br>4+ | IFI<br>FUL | OTF<br>MT | OTF<br>4+ | OTF<br>FUL |

The bits shown as zeros in the proceeding bit layout must be set to zeros when writing to the Bus Master Control/Status Register. The bits that have non-zero indications are the only useful bits in this register. The remaining bits are reserved for diagnostic purposes. Even though some of these bits are shown as zeros, they may eventually be read as ones. Note that the Inbound FIFO refers to the internal PCI controller interface chips' FIFO for executing highway read operations and the Outbound FIFO refers to highway write operations.

| <31:28> | These bits are not used but must be written to zero.                                                                                                         |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <27>    | MAILBOX FLAG RESET is a write-only bit that resets all of the mailbox status flags.                                                                          |

| <26>    | INBOUND FIFO RESET is a write-only bit which clears the inbound FIFO, Inbound FIFO +4 bit, Inbound FIFO Full and sets the Inbound FIFO Empty flag.           |

| <25>    | OUTBOUND FIFO RESET is a write-only bit which clears the outbound FIFO,<br>Outbound FIFO +4 bit, Outbound FIFO Full and sets the Outbound FIFO<br>Empty bit. |

| <24>    | ADD-ON RESET is a write-only bit which, when set to a one, resets all of the Highway Operational Registers.                                                  |

| <23:6>  | These bits are not used but must be written to zero.                                                                                                         |

| <5>     | INBOUND FIFO EMPTY is a read-only bit that is set when the inbound FIFO contains no data.                                                                    |

| <4>     | INBOUND FIFO +4 is a read-only bit and is set to a one as long as there are at least 4 longwords of data in the inbound FIFO.                                |

| <3>     | INBOUND FIFO FULL is a read-only bit that is set when the incoming FIFO is full.                                                                             |

| <2>     | OUTBOUND FIFO EMPTY is a read-only bit that is set when the outbound FIFO contains no data.                                                                  |

| <1>     | OUTBOUND FIFO +4 is a read-only bit and is set to a one as long as there are at least 4 longwords of data in the outbound FIFO.                              |

| <0>     | OUTBOUND FIFO FULL is a read-only bit that is set when the outbound FIFO is full.                                                                            |

## HIGHWAY OPERATIONAL REGISTERS

The following section describes the registers used to control operations directed toward the Interconnect Highway. The base address of these registers is set dynamically when the computer is powered-up and the PCI BIOS is executed. The PCI BIOS determines the resources required by each add-in card and allocates memory and I/O addresses accordingly. After the setup has been completed, the Base Address Register #2 from the PCI Interface Registers may be read to determine the address allocated to the V122 by the PCI BIOS.

| Address                           | Register<br>Description              | Mnemonic |

|-----------------------------------|--------------------------------------|----------|

| Base + 00                         | Control/Status Register              | CSR      |

| Base + 04                         | Interrupt<br>Control/Status Register | ICSR     |

| Base + 08                         | Timer Control Register               | ICR      |

| Base + OC                         | Command Memory Address<br>Register   | CMA      |

| Base + 10                         | Command Memory Data<br>Register      | CMD      |

| Base + 14                         | List Transfer Count<br>Register      | LTCR     |

| Base + 18                         | Total Transfer Count<br>Register     | TTCR     |

| Base + 1C                         | Memory Address Register              | MAR      |

| Base + 20                         | Reserved                             | RSVD     |

| Base + 24                         | Reserved                             | RSVD     |

| Base + 28                         | Demand FIFO Register                 | DFR      |

| Base + 2C                         | Reset Interface                      | RSTIFC   |

| Base + 30                         | Reset Demand FIFO                    | RSTDFR   |

| Base + 34<br>through<br>Base + 3F | Reserved                             |          |

Appendix A contains a composite register layout chart for the V122.

#### **Control/Status Register**

The Control/Status Register (CSR) is a write/read register located at an offset of 0 from the selected base address. This register is used to control and monitor various operations occurring within the V122 and on the Interconnect Highway. Since this register contains read-only, write-only, and write/read bits, two bit patterns are shown. Those bits that are shown as zero for the write layout must be set to zero when writing to this register.

Control/Status Register(CSR)

Write Operations:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Model V122

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05                  | 04                 | 03                 | 02                 | 01       | 00 |

|----|----|----|----|----|----|----|----|----|----|---------------------|--------------------|--------------------|--------------------|----------|----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AP<br>ND<br>ST<br>A | RL<br>D<br>EN<br>A | DM<br>A<br>DI<br>R | DM<br>A<br>EN<br>A | SU<br>SP | GO |

**Read Operations:**

| 31                 | 30                 | 29                  | 28                  | 27                 | 26       | 25                  | 24                 | 23       | 22             | 21                   | 20                 | 19                 | 18                 | 17       | 16       |

|--------------------|--------------------|---------------------|---------------------|--------------------|----------|---------------------|--------------------|----------|----------------|----------------------|--------------------|--------------------|--------------------|----------|----------|

| ER<br>R<br>CD<br>3 | ER<br>R<br>CD<br>2 | ER<br>R<br>CD<br>1  | ER<br>R<br>CD<br>0  | VX<br>I<br>TM<br>O | RS<br>VD | RS<br>VD            | RS<br>VD           | RS<br>VD | NO<br>SY<br>NC | 0                    | PA<br>R<br>ER<br>R | RS<br>VD           | RS<br>VD           | RS<br>VD | RS<br>VD |

| 15                 | 14                 | 13                  | 12                  | 11                 | 10       | 09                  | 08                 | 07       | 06             | 05                   | 04                 | 03                 | 02                 | 01       | 00       |

| 0                  | 0                  | LI<br>ST<br>IN<br>T | DM<br>D<br>OF<br>LO | DM<br>D<br>PN<br>D | 0        | XM<br>T<br>FU<br>LL | RC<br>V<br>DA<br>V | DO<br>NE | 0              | AP<br>ND<br>ST<br>AT | RL<br>D<br>EN<br>A | DM<br>A<br>DI<br>R | DM<br>A<br>EN<br>A | SU<br>SP | 0        |

<31:28> ERROR CODE3 through 0 are read-only bits that encode the source of a V122 error. The following chart shows the error code hex pattern along with the source of the error. The error sources are encoded by a priority encoder resulting in the highest priority error being displayed in the case where multiple errors are encountered. Individual bits in the CSR may be read to determine other error sources that may have occurred along with the highest priority error encoded.

#### Error Code Error Source

- F Reserved.

- E Reserved.

- D PARITY ERROR. The V122 highway receiver detected a parity error on the incoming message.

- C ADDRESS\_NOT\_RECOGNIZED. An addressed highway command message was transmitted by the V122 and then received by the V122 indicating that the addressed slave did not accept the message.

- B TIMEOUT. A highway command message was transmitted by the V122 and a reply message was not received within the preselected timeout period.

- A VXI TIMEOUT. A VXI bus timeout occurred in the VXI chassis addressed during the last highway operation.

- 9 Reserved.

- 8 Reserved

- 7 Reserved

- 6 Reserved

- 5 Reserved

|       | 4                           |                                                   | ILLEGAL COMMAND. This error code is generated when an attempt is made at accessing a non-existent location within a VXI controller.                                                                                                                                                                                                                                                                                                                                                              |

|-------|-----------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 3                           |                                                   | REMOTE PARITY ERROR. This code is generated when an addressed slave receives a parity error.                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | <b>Error</b><br>2<br>1<br>0 | Code                                              | Error Source<br>Reserved.<br>Reserved.<br>NO ERROR. There are no errors to report from the V122.                                                                                                                                                                                                                                                                                                                                                                                                 |

| < 27> |                             |                                                   | ME TIMEOUT is a read-only bit that is set when an operation in an ssed VXI/VME chassis resulted in a bus timeout.                                                                                                                                                                                                                                                                                                                                                                                |

| < 26> |                             | Reserv                                            | zed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| < 25> |                             | Reserv                                            | ved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| < 24> |                             |                                                   | GAL COMMAND is a read-only bit that is set when an attempt is made to<br>a non-existent address location within a CAMAC or VXI controller.                                                                                                                                                                                                                                                                                                                                                       |

| < 23> |                             |                                                   | OTE PARITY ERROR is a read-only bit that is set when an addressed receives a parity error.                                                                                                                                                                                                                                                                                                                                                                                                       |

| < 22> |                             | receivi<br>operat<br>highwa<br>large k<br>large d | XNC is a read-only bit that is set when the V122 highway driver is not<br>ing a synchronization message from the highway. When no list processing<br>ions are occurring, the V122 sends a synchronization message around the<br>ay, expecting to see it returned. The SYNC LED may not be lit during<br>plock transfer operations since the sync message is not inserted during<br>lata transfers. A loss of the SYNC signal during large data transfers does<br>t any NO SYNC error conditions. |

| < 21> |                             | This b                                            | it is not used and is read as a zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| < 20> |                             |                                                   | TY ERROR is a read-only bit that is set when the V122 receives a message ontains a parity error.                                                                                                                                                                                                                                                                                                                                                                                                 |

| <19>  |                             | messa                                             | OUT is a read-only bit that is set when the V122 transmits a command<br>ge to a slave and the slave does not respond within the selectable timeout<br>. This period can range from 3 to 10 seconds.                                                                                                                                                                                                                                                                                              |

| < 18> |                             | transn                                            | ESS_NOT_RECOGNIZED is a read-only bit that is set when the V122 nits a command message to a slave and receives the message back ting that the addressed slave did not respond.                                                                                                                                                                                                                                                                                                                   |

- <17> Reserved

- < 16> Reserved

- <15:14> These bits are not used and are read as zeros.

- <13 > LIST INTERRUPT is a read-only bit that is set when the list processing DSP asserts an interrupt to the host computer. This bit also appears in the Interrupt Control/Status Register.

- < 12> DEMAND OVERFLOW is a read-only bit that is set when the V122 has 2048 demands pending in the Demand FIFO Register and a subsequent demand message is received. This bit may be cleared by a write operation to the Clear Demand FIFO Register address.

- < 11> DEMAND PENDING is a read-only bit that is set when at least one demand message is contained in the Demand FIFO Register.

- < 10> This bit is not used and is read as a zero.

- < 9> TRANSMIT FULL is a read-only bit that reflects the status of the highway transmitter write data FIFO. The full flag is used to determine if the FIFO may accept additional write data words when executing programmed I/O highway operations. As long as this bit is zero, the FIFO may be written.

- < 8> RECEIVE DATA AVAILABLE is a read-only bit that is set to a one as long as highway read data is contained in the read data FIFO. This bit is used for programmed I/O read operations for determining data availability.

- < 7> DONE is a read-only bit that indicates when the V122 is not executing any list operations. Once a list operation is initiated, the DONE bit is set to a zero until the operation is completed.

- <6> This bit is not used and is read as a zero.

- <5> APPEND STATUS is a write/read bit that enables and disables the appending of a status word after a list execution terminates. Setting this bit to a one enables the status append and a zero disables the function. Refer to the Append Status section of this manual for additional information.

- <4> Reserved

- <3> DMA DIRECTION is a write/read bit that specifies the direction of DMA transfers. A direction of zero specifies DMA transfers from host memory to the

V122 (write operations). A one specifies DMA transfers from the V122 to host memory (read operations).

- < 2> DMA ENABLE is a write/read bit that is used to enable/disable DMA activity. Setting this bit to a one enables DMA operations to occur when the list processor requests data transfers. A zero allows for programmed I/O transfers and disables DMA operations.

- < 1> SUSPEND is a write/read bit used to suspend list processing operations in the V122. After SUSPEND is set to a one, the host must wait for the DONE bit to be set before using the V122 for other operations. After the DONE bit has been set, the SUSPEND bit may then be written back to a zero.

- < 0> GO is a write-only bit that is used to initiate list-processing operations at the address specified in the List Memory Address Register.

## Interrupt Control/Status Register

The Interrupt Configuration Register (ICSR) is a write/read register located at an offset of 4 from the selected base address. This register is used to enable/disable the various sources of interrupts on the V122. Status bits are also in this register reflecting the state of the interrupt sources. Once enabled and sourced, the V122 asserts the PCI INTA signal to the host.

The V122 has five sources of interrupts as follows:

- 1.) List Processing Done

- 2.) List Interrupt

- 3.) Demand

- 4.) A PCI Interface Controller Interrupt.

The ICSR contains individual enables and status bits for each of the five sources. To allow an interrupt status bit to be enabled in the ICSR, the corresponding enable bit must be set to a one. Interrupt sources are disabled by setting the bit to a zero. In the case where polling is used

instead of interrupt generation, the interrupt source bits may be cleared by writing to the ICSR with the data set equal to the source bit to be cleared.

The following diagram shows the bit layout of the Interrupt Control/Status Register.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|    |    |    |    | •  |    |    |    |    |    |    |    | •  |    |    |    |

| 15 | 14 | 13 | 12 |    | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | UI | 00 |

#### Interrupt Control/Status Register (ICSR)

| 0 0     | 0 0 0 0 0 PC RS DM LI DO PC RS DM LI DO<br>I VD D ST NE I VD D ST NE<br>IN IN IN IN IE IE IE IE<br>T T T T T I                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

| <31:10> | These bits are not used and read as zero.                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| < 9>    | PCI INTERFACE INTERRUPT SOURCE is a read only bit that reflects the status of the PCI interface chips' interrupt source. The actual source of these interrupts may be found in the PCI Interrupt Control/Status Register.                                                                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| < 8>    | Reserved                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| < 7>    | DEMAND INTERRUPT SOURCE is a read/write-to-clear bit that is set<br>whenever a demand message is received by the V122 and this interrupt source is<br>enabled. A write of this bit with data set to one clears the source. The DMD IE<br>bit in this register must be set to a one to enable this interrupt source. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| < 6>    | LIST INTERRUPT SOURCE is a read/write-to-clear bit that is set when the list<br>processor executes a Generate Host Interrupt instruction. A write of this bit<br>with data set to one clears the source. The LIST IE bit in this register must be<br>set to a one to enable this interrupt source.                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| < 5>    | DONE INTERRUPT SOURCE is a write/read bit that is set when the V122 completes execution of a list and this interrupt source is enabled. A write of this bit with data set to a one clears the source. The DONE IE bit in this register must be set to a one to enable this source.                                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| < 4>    | PCI INTERFACE INTERRUPT ENABLE is a write/read bit that is used to<br>enable/disable the generation of a PCI interrupt request when the PCI Interface<br>chip requires service. Setting this bit to a one enables the interrupt source and<br>a zero disables the source.                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| < 3>    | Reserved                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| < 2>    | DEMAND INTERRUPT SOURCE ENABLE is a write/read bit that<br>enables/disables the generation of an interrupt source when the V122 receives a<br>demand message from the highway. Setting this bit to a one enables the<br>interrupt source and a zero disables the source.                                            |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| <1>     | LIST INTERRUPT SOURCE ENABLE is a write/read bit used to enable/disable<br>the assertion of an interrupt source when the list processor executes a Generate<br>Host Interrupt instruction. Setting this bit to a one enables the interrupt source<br>and a zero disables the source.                                |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

<0> DONE INTERRUPT SOURCE ENABLE is a write/read bit used to enable/disable the generation of an interrupt source when a list processing operation completes. Setting this bit to a one enables the interrupt source and a zero disables the source.

## Timer Control Register

The Timer Control Register (TCR) is a write/read register located at an offset of 08 hex from the selected base address. This register is used to specify the frequency at which list execution is initiated during timer initiated list processing operations.

The timer frequency can range from 250 Kilohertz to .059 hertz. This range yields 'tic' rates (periods) from 40 microseconds to 16.777 seconds in 1 microsecond increments. This timer rate specification does not refer to the interval at which each element in the list is executed but the rate at which the entire list is initiated. This automatic mode is enabled with bit 24 in this register.

The V122 provides for an external clock input that controls the rate at which the list is started. This input is routed through the external clock LEMO connector mounted on the front panel of the V122. The clock period may range from 250 kHz to DC. The input signal is low true and must have a minimum pulse width of 200 nanoseconds and a maximum of 1 microsecond.

If the timer rate selected for list execution is faster than the time it takes to execute the entire list, the clock transitions that occur while the list is executing are ignored.

The data for this register is calculated as follows:

((1/Desired Frequency)/1 X 10<sup>-6</sup>) -1

The following diagram shows the bit layout of the Timer Control Register.

Timer Control Register (TCR)

| 31        | 30        | 29        | 28        | 27        | 26        | 25         | 24         | 23        | 22        | 21        | 20        | 19        | 18        | 17        | 16        |

|-----------|-----------|-----------|-----------|-----------|-----------|------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0         | 0         | 0         | 0         | 0         | 0         | CLK<br>SRC | TMR<br>ENA | TCR<br>23 | TCR<br>22 | TCR<br>21 | TCR<br>20 | TCR<br>19 | TCR<br>18 | TCR<br>17 | TCR<br>16 |

| 15        | 14        | 13        | 12        | 11        | 10        | 09         | 08         | 07        | 06        | 05        | 04        | 03        | 02        | 01        | 00        |

| TCR<br>15 | TCR<br>14 | TCR<br>13 | TCR<br>12 | TCR<br>11 | TCR<br>10 | TCR<br>9   | TCR<br>8   | TCR<br>7  | TCR<br>6  | TCR<br>5  | TCR<br>4  | TCR<br>3  | TCR<br>2  | TCR<br>1  | TCR<br>0  |

<31:26> These bits are not used and are read as zeros.

<25> CLOCK SOURCE is a write/read bit that selects the source of the timing signal that initiates list execution when the TMR ENA bit is set to a one. Setting the

CLK SRC bit to a one selects the external clock input and a zero selects the internal timer.

- <24> TIMER ENABLE is a write/read bit that is used to enable/disable timer initiated list-processing operations. Setting this bit to a one enables timer initiated operations and a zero disables timer operations.

- <23:0> TIMER CONTROL RATE23 through 0 are write/read bits that are used to select the rate at which list processing operations are initiated when the timer operations are enabled. The least significant bit of this field corresponds to a 1microsecond interval. The data loaded in this register is actually one less than the desired interval. For example, to select a 250-microsecond interval, load the value 249 into this register.

## **Command Memory Address Register**

The Command Memory Address Register (CMA) is a write/read register located at an offset of OC Hex from the selected base address. This register is used for several purposes. The CMA is used to specify the start address for list processing, specify the memory address at which subsequent write/read operations to the Command Memory Data Register occur, and to read the last address that the list processor accessed during a list processing operation.

The Command Memory Data Register (CMD) is a 32K X 32 memory that is used to hold the list processing instructions to be executed. The CMD is loaded by executing programmed I/O write operations to offset 10 Hex. Prior to executing the initial write to the memory, the CMA must first be loaded with the first address location to access. The valid address range is 0 to 7FFF Hex. After the CMA is loaded, the first CMD data word may then be written. After a write operation to the CMD, the CMA is automatically incremented to the next address location. This allows the CMD to be loaded without having to write the CMA for every CMD write operation.

If it is necessary to read the CMD, the CMA must first be loaded with the initial address to be accessed. After a word of data is read from the CMD, the CMA is automatically incremented to the next address location.

A bit in this register is also provided which initiates a single list processing operation. Setting this bit causes the same operation as setting the GO bit in the Control/Status Register. The format of the Command Memory Address Register is shown in the following diagram.

| <br>31         | 30            | 29            | 28            | 27            | 26            | 25           | 24           | 23           | 22           | 21           | 20           | 19           | 18           | 17           | 16           |

|----------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| 0              | 0             | 0             | 0             | 0             | 0             | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            |

| 15             | 14            | 13            | 12            | 11            | 10            | 09           | 08           | 07           | 06           | 05           | 04           | 03           | 02           | 01           | 00           |

| LI<br>ST<br>GO | CM<br>A<br>14 | CM<br>A<br>13 | CM<br>A<br>12 | CM<br>A<br>11 | CM<br>A<br>10 | CM<br>A<br>9 | CM<br>A<br>8 | CM<br>A<br>7 | CM<br>A<br>6 | CM<br>A<br>5 | CM<br>A<br>4 | CM<br>A<br>3 | CM<br>A<br>2 | CM<br>A<br>1 | CM<br>A<br>0 |

<31:16> These bits are not used and are read as zeros.

<15> LIST GO is a write-only bit that is set to a one to initiate a list processing operation. Setting this bit has the same effect as setting the GO bit in the CSR. This bit is not latched.

<14:0> COMMAND MEMORY ADDRESS14 through 0 are used for specifying the initial address for CMD write/read operations, the initial address for list

execution, and for determining where the list processor halted after list processing.

## **Command Memory Data Register**

The Command Memory Data Register (CMD) is a write/read register located at an offset of 10 Hex from the selected base address. This register is used to load the instructions for the list processor. The format of these instructions/commands may be found in the Command Memory Instructions section of this manual.

The Command Memory is a 32K X 32 memory that is accessed by programmed I/O. Before initial words may be written to the CMD, the Command Memory Address Register (CMA) must be loaded. After the CMA is loaded with the first address of the CMD to access, the CMD may then be written. After a write operation to the CMD, the CMA is automatically incremented to the next sequential address location. This eliminates the need to reload the CMA for every access to the CMD.

If necessary, the CMD may be read to verify its contents. As with write operations to the CMD, the CMA must be loaded prior to the initial access to the CMD. After a read operation is executed to the CMD, the CMA is automatically incremented.

The format of the Command Memory Data Register is shown in the following diagram.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| CM |

| D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  |

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

| CM |

| D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

Command Memory Data Register

<31:0> COMMAND MEMORY DATA31 through 0 are write/read bits used to load/read the 32K X 32 Command Memory.

## List Transfer Count Register

The List Transfer Count Register (LTCR) is a read-only register located at an offset of 14 Hex from the selected base address. This register returns the two's complement of the number of transfers remaining during a block transfer mode of operation. When the list processor encounters a block transfer instruction, it loads the 32-bit List Transfer Count Register with the count specified in the instruction. This value is the two's complement of the maximum

number of transfers that are to occur for the block transfer operation. When this counter is incremented to zero, the block transfer operation terminates and the next instruction in the list is interpreted. If an error occurs during the block operation, the LTCR may then be read to determine the number of transfers remaining. The Transfer Count reflects the number of transfers without regard to the data word size.

The following diagram shows the bit pattern for the List Transfer Count Register.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| LT |

| C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  |

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

| LT |

| C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  | C  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

<31:0> LIST TRANSFER COUNT31 through 0 are read-only bits That reflect the number of transfers remaining after a block transfer operation concludes. This data is in two's complement format.

## **Total Transfer Count Register**

The Total Transfer Count Register (TTCR) is a write/read register located at an offset of 18 Hex from the selected base address. This register is used to specify the maximum number of DMA transfers that are to occur. Before a list operation is executed where data transfers to/from the

highway occur using Direct Memory Access (DMA), the Total Transfer Count Register must be loaded with the two's complement of the maximum number of transfers. In case that the list terminates prematurely, the TTCR may be read to determine the number of transfers remaining to be executed.

Along with write access to the TTCR from the host by programmed I/O, the TTCR may also be loaded by using a list instruction. When the list processor encounters this instruction, the contents of the count specification are loaded into the TTCR.

The TTCR is incremented once for every DMA write or read access to PCI. When the counter increments to zero, the transfer is considered complete.

The following diagram shows the bit layout for the Total Transfer Count Register.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| TT |

Model V122

| CR |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

| TT |

| CR |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

<31:0> TOTAL TRANSFER COUNT31 through 0 are write/read bits which specify the maximum number of DMA transfers to execute. A read of this register returns the two's complement of the number of transfer remaining.

## Memory Address Register

The Memory Address Register (MAR) is a write/read register located at an offset of 1C Hex from the selected base address. This register is used to specify the initial Direct Memory Access (DMA) address. Before any DMA operations are executed by the V122, the MAR must be loaded with the first address to be accessed during DMA write or read operations. After the V122 executes the first DMA operation, the MAR is automatically incremented to the next sequential longword address. Note that all DMA MAR specifications must be longword aligned.

DMA operations to/from the V122 are always 32-bits in length. Therefore, the MAR specification must be on a longword boundary.

| 31            | 30            | 29            | 28            | 27            | 26            | 25            | 24            | 23            | 22            | 21            | 20            | 19            | 18            | 17            | 16            |

|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| MA<br>R<br>31 | MA<br>R<br>30 | MA<br>R<br>29 | MA<br>R<br>28 | MA<br>R<br>27 | MA<br>R<br>26 | MA<br>R<br>25 | MA<br>R<br>24 | MA<br>R<br>23 | MA<br>R<br>22 | MA<br>R<br>21 | MA<br>R<br>20 | MA<br>R<br>19 | MA<br>R<br>18 | MA<br>R<br>17 | MA<br>R<br>16 |

| 15            | 14            | 13            | 12            | 11            | 10            | 09            | 08            | 07            | 06            | 05            | 04            | 03            | 02            | 01            | 00            |

| MA<br>R<br>15 | MA<br>R<br>14 | MA<br>R<br>13 | MA<br>R<br>12 | MA<br>R<br>11 | MA<br>R<br>10 | MA<br>R<br>9  | MA<br>R<br>8  | MA<br>R<br>7  | MA<br>R<br>6  | MA<br>R<br>5  | MA<br>R<br>4  | MA<br>R<br>3  | MA<br>R<br>2  | 0             | 0             |

# <31:2> MEMORY ADDRESS31 through 2 are write/read bits used to specify the initial DMA Memory Address.

<1:0> These bits are not used and are read as zeros.

## **Demand FIFO Register**

The Demand FIFO Register (DFR) is a read-only register located at an offset of 28 Hex from the selected base address. This register is loaded with demand message data received from the highway. When a slave chassis requires service, it may generate an asynchronous demand message on the highway. When the V122 receives these demands, they are placed in a 2K X 16 FIFO. Optionally, the V122 may assert a PCI interrupt when the V122 receives a demand message. The FIFO data contains the node address of the chassis that generated the demand message along with an 8-bit identifier. Please refer to the individual slave module manuals for details on the sources of the identifiers.

As long as there is at least one demand message contained in the Demand FIFO Register the DEMAND PENDING (DMD PND) bit in the CSR is set to a one. If the DFR is full (2048 demands) and an additional demand message is received from the highway, the DEMAND OVERFLOW (DMD OFL) bit in the CSR is set to a one. The Demand FIFO Register and the DEMAND OVERFLOW bit are cleared by power-up, a write to the Reset Interface address, and by a write to the Reset Demand FIFO address.

The following diagram shows the bit pattern for the Demand FIFO Register.

| 31 | 30            | 29            | 28            | 27           | 26           | 25           | 24           | 23           | 22           | 21           | 20           | 19           | 18           | 17           | 16           |

|----|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| 0  | 0             | 0             | 0             | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            |

| 15 | 14            | 13            | 12            | 11           | 10           | 09           | 08           | 07           | 06           | 05           | 04           | 03           | 02           | 01           | 00           |

| 0  | ND<br>A<br>64 | ND<br>A<br>32 | ND<br>A<br>16 | ND<br>A<br>8 | ND<br>A<br>4 | ND<br>A<br>2 | ND<br>A<br>1 | DI<br>D<br>7 | DI<br>D<br>6 | DI<br>D<br>5 | DI<br>D<br>4 | DI<br>D<br>3 | DI<br>D<br>2 | DI<br>D<br>1 | DI<br>D<br>O |

<31:15> These bits are not used and are read as zeros.

- <14:8> NODE ADDRESS64 through 1 are read-only bits which indicates the chassis' node address that generated the demand message.

- <7:0> DEMAND IDENTIFIER7 through 0 are read-only bits which indicate the chassis' internal demand source.

## **Reset Interface**

The Reset Interface (RSTIFC) is a write-only address location located at an offset of 2C Hex from the selected base address. A write operation to this address with any data pattern causes the V122 to be reset to an initial state.

# **Reset Demand FIFO Register**

The Reset Demand FIFO Register is a write-only address location located at an offset of 30 Hex from the selected base address. A write operation to this address with any data pattern causes the Demand FIFO Register and the DEMAND OVERFLOW bit to be cleared.

## **PROGRAMMED TRANSFERS**

Programmed transfers are used to setup and initiate highway operations. Once these operations are started, data transfer to/from the Data FIFO Registers may occur under programmed transfer or by Direct Memory Access (DMA). DMA transfers have a significant speed advantage over programmed transfers. The DMA transfers to the V122 occur without any software overhead once the transfer is setup.

When using programmed transfers, the software must examine the FIFO flags in order to determine whether to transfer data to/from the Data FIFO Resister (FIFO). These flags are located in the Control/Status Register of the Highway Operational Registers and the Bus Master Control/Status Register of the PCI Interface Registers. Before a write operation to the V122 FIFOs may occur, the software must read the Control/Status Register (CSR) to determine if there is room in the FIFO for another piece of write data. If either the TRANSMIT FIFO FULL bit in the Control/Status Register is set or the OUTBOUND FIFO FULL bit in the Bus Master Control/Status Register is set, the software must suspend the write operation until both bits are negated. When read commands are executed, the software must first check the INBOUND FIFO EMPTY bit in the Bus Master Control/Status Register before the data may be retrieved. If this bit is set, the software must loop on reading these registers until the bit is asserted. These procedures must be followed when executing programmed transfer operations to the FIFO while list processing is in progress.

The following is a basic example of how to execute a programmed transfer list operation. For this example, the direction of data transfer is from the 2960 to a highway slave device.

- 1.) Set the Command Memory Address Register to zero.

- 2.) Load the Command Memory Data Register with the instructions required to execute the write operation. Make sure that the last element in the list is a HALT instruction.

- 3.) Set the Command Memory Address Register to zero.

- 4.) Set the GO bit in the Control/Status Register.

- 5.) Read the Control/Status Register and loop on this step until the TRANSMIT FIFO FULL bit is false.

- 6.) Read the Bus Master Control/Status Register and loop on this step until the OUTBOUND FIFO FULL bit is false.

- 7.) Write the Data FIFO Register with the data to be transmitted. Return to step 5 until all the transmit data words have been loaded into the V122.

- \* 8.) Wait for the DONE bit in the Control/Status Register to be asserted, indicating that the operation is complete.

9.) Read the Control/Status Register and Error/Status Register to check for any errors.

The following example shows the steps required to execute a programmed transfer operation that transfers data from a highway slave device to the 2960.

- 1.) Set the Command Memory Address Register to zero.

- 2.) Load the Command Memory Data Register with the instructions required to execute the write operation. Make sure that the last element in the list is a HALT instruction.

- 3.) Set the Command Memory Address Register to zero.

- 4.) Set the GO bit in the Control/Status Register.

- 5.) Loop on reading the Control/Status Register until the Bus Master Control/Status Register until the INBOUND FIFO EMPTY bit is set.

- 6.) Read the data from the Data FIFO Register and return to step 5 until all data words have been read.

- 7.) Wait for the DONE bit in the Control/Status Register to be asserted indicating that the operation is complete.