# KineticSystems' Model

© Copyright 2006, 2007 DynamicSignals LLC. All rights reserved.

DynamicSignals LLC makes no representations that the use of its products in manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of license to make, use, or sell equipment or software in accordance with the description.

No part of this publication may be reproduced, transmitted, or stored in any form, or by any means without the written permission of DynamicSignals.

Technical specifications contained within this publication are subject to change without notice.

V155 User's Manual Release 1.0

## **Table Of Contents**

| Chapter 1: Introduction                                            | 1    |

|--------------------------------------------------------------------|------|

| Description                                                        | 1    |

| V155 Specifications                                                | 1    |

| Front Panel                                                        |      |

| Product Ordering Information                                       | 3    |

| Related Products                                                   |      |

| Chapter 2: Installation and Configuration                          | 4    |

| Unpacking the V155                                                 | 4    |

| Selecting Slot-0 Operation                                         |      |

| Selecting Non Slot-0 Operation                                     |      |

| Setting the Logical Address                                        |      |

| Installation                                                       |      |

| Module Installation                                                |      |

| Operating System Installation                                      |      |

| Software Installation                                              |      |

| Chapter3: VXIbus Configuration Registers and Operational Registers |      |

| ID/Logical Address Register                                        |      |

| Device Type Register                                               |      |

| Status/Control Register                                            |      |

| MODID Register                                                     |      |

| Suffix High Register                                               |      |

| Suffix Low Register                                                |      |

| Serial Number High Register                                        |      |

| Serial Number Low Register                                         |      |

| Interrupt Status Register                                          | .21  |

| Interrupt Control Register                                         |      |

| Trigger Interrupt Mask/Trigger Interrupt Source Register           |      |

| Trigger Interrupt Source Clear Register                            |      |

| Trigger Source Register                                            |      |

| Trigger Timer Configuration Register                               | .30  |

| SBC Slave Mode Enable Register                                     | . 33 |

| Interrupt Status ID Register.                                      | .34  |

| Miscellaneous Control Register                                     | . 35 |

| Chapter 4: Programming                                             |      |

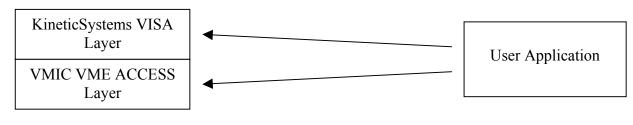

| Software Layers                                                    | .36  |

| VMIC VME Layer                                                     | . 36 |

| KineticSystems VISA Layer                                          | . 36 |

| Example                                                            | . 36 |

| Building an application                                            | .38  |

| Chapter 5: VXI Triggers                                            |      |

| Synchronous Trigger Example:                                       | . 39 |

| Start/Stop Trigger Example:                                        | .39  |

| Appendix A                     | . 44 |

|--------------------------------|------|

| Technical Support and Warranty |      |

| Feedback                       |      |

## **Chapter 1: Introduction**

## Description

The V155 is a single-width, C-size module that combines the performance of a Pentium Mbased computer with the functionality of a VXI Slot-0 controller. Alternatively, on-board strap options enable this module to be used as a VXI-based processor in non-Slot-0 applications.

The V155's optional External CD-ROM drive allows for the installation of a number of popular programming environments and compilers, including Microsoft Visual C++, Borland C++, and Microsoft Visual Basic.

For soft real-time applications, the V155 coupled with the Windows XP Pro operating system is a cost-effective and high-performance Slot-0 controller solution for your data collection needs.

## **V155 Specifications**

| Item                         | Specification                                                                    |

|------------------------------|----------------------------------------------------------------------------------|

| Processor Options            | Pentium M Processor 1.1 GHz                                                      |

|                              | Pentium M Processor 1.6 GHz                                                      |

|                              | Pentium M Processor 1.8 GHz                                                      |

| DDR SDRAM                    | Options available with 512Mbyte, 1Gbyte and 1.5Gbyte                             |

| Internal Hard Drive          | 40 GB IDE Hard Drive, contact KineticSystems for latest hard drive offerings     |

| Timers and Watchdog Timer    | Two 16-bit timers and two 32-bit timers and software programmable watchdog timer |

| Compact Flash Memory         | Supports up to 2 GB of Compact Flash through secondary IDE port                  |

| RTC/NVSRAM                   | Real Time Clock and 32 KB of nonvolatile SRAM                                    |

| Ethernet Interface           | Dual Ethernet controllers supporting 10BaseT, 100BaseTX and 1000BaseT interfaces |

| PMC Slot                     | 5 V signaling, types 1 and 2, 32-bit PCI bus, 66 MHz maximum                     |

| AGP Support                  | Internal AGP SVGA controller and Digital Visual Interface (DVI)                  |

| USB Port                     | Supports 2 USB Rev. 2.0                                                          |

| Environmental and Mechanical |                                                                                  |

| Temperature Range            |                                                                                  |

| Operational                  | 0 to +50 degrees C                                                               |

| Storage                      | -25 to 75 degrees C                                                              |

| Relative Humidity            | 0 to 86% non-condensing to 40 degrees C                                          |

| Vibration and Shock          |                                                                                  |

| Operating Vibration          | 9.8m/s <sup>2</sup> (1.0G), 5-500 Hz                                             |

| Operating Shock              | 1470m/s <sup>2</sup> (150G)                                                      |

| Non-Operating Shock          | 6860m/s <sup>2</sup> (700G)                                                      |

| Power Requirements           |                                                                                  |

| +5V                          | 9500 mA                                                                          |

| -5.2V                        | 270 mA                                                                           |

| -2V                          | 96 mA                                                                            |

| +12V                         | 100 mA                                                                           |

| -12V                         | 100 mA                                                                           |

Technical specifications contained within this publication are subject to change without notice.

Table 1-1. Specifications

## **Front Panel**

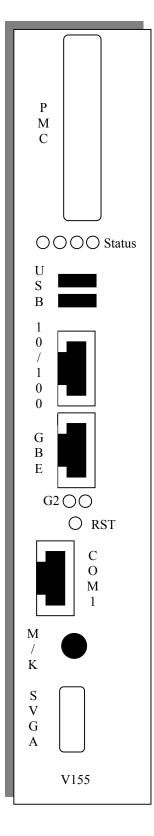

The V155 font-panel has all the standard external connections for monitor, mouse, keyboard, Ethernet, USB, and COM ports.

- I PMC site for high speed reflective memory or high speed digital I/O.

- > The 4 Status LEDs (from left to right) indicate:

- Boot LED—indicates BIOS boot in progress (red)

- Power LED—indicates when power is applied; also indicates throttling by blinking slowly (green)

- IDE LED—indicates when IDE activity is occurring (yellow)

- VME LED—indicates VME SYSFAIL condition (red)

- > 2 USB ports support standard USB Interface Rev 2.0

- > 2 Ethernet ports:

- 10/100—supports 10BaseT and 100BaseTX Ethernet options.

- GBE—supports 10BaseT, 100BaseTX and Gigabit Ethernet options.

- Gigabit Ethernet LEDs

- The recessed RST button applies SYSRESET to the VME backplane and resets (reboots) the SBC microprocessor.

- > 1 RJ45 connector16550-compatible serial port.

- > 1 6-pin PS-2 combined keyboard and mouse connector.

- > 1 standard SVGA video connector.

## **Product Ordering Information**

Model

V155-AB14

VMIC 7807 P4, 1.8 GHz, 1.5 GB, 40 GB Hard Disk

Model

V155-AB13

VMIC 7807 P4, 1.8 GHz, 1 GB, 40 GB Hard Disk

Model

V155-AB12

VMIC 7807 P4, 1.8 GHz, 512 MB, 40 GB Hard Disk

### **Related Products**

V155-EXCD External CD-ROM USB

V155-KBMS Keyboard and Mouse

LX40-ALA6 KineticSystems VISA Library

DX10-ALA6 VMIC Plug-In Driver

V155-OSIN Windows XP Pro Installed on Hard Disk

V155-BSP VMIC Board Support Package

## **Chapter 2: Installation and Configuration**

## **Unpacking the V155**

The Model V155 is shipped in an anti-static bag with a Styrofoam packing container. Carefully remove the module from its anti-static bag and prepare to set the various options to conform to the operating environment. Make sure that all anti-static precautions are taken to avoid damaging the module. Please take the following precautions when unpacking the module:

- When handling module, use a grounding strap or touch a grounded object.

- Touch the anti-static package to a metal part of your VXI chassis before removing the module from the package.

- Remove the module from the package and inspect the module for damage.

- Do not install the module into the VXI chassis until you are satisfied that the module exhibits no obvious mechanical damage and is configured to conform to the desiring operating environment.

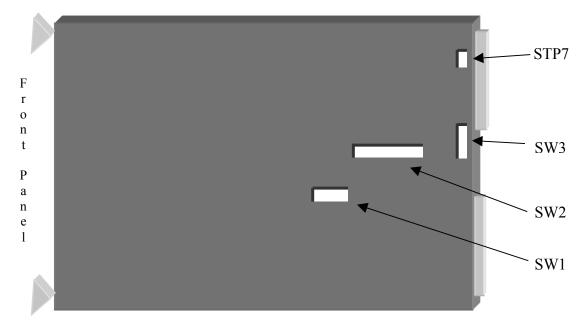

The V155 requires various strap and switch selections to be set before installing the module in the VXI chassis, located as follows:

The V155 may be configured to operate as either a Slot0 controller or a non-Slot0 controller. When the V155 is the Slot0 controller, it must be located in the left-most slot (Slot0) and be set for Logical Address 0. If the V155 is not the Slot0 controller, it may be located in any other slot in the chassis and set for Logical Address 1 through 255. Selection of Slot-0/Non Slot-0 operation is made via settings of the SW1, SW3, and STP7 settings, as described below. By default, the V155 is shipped from the factory configured as a slot-0 controller.

## **Selecting Slot-0 Operation**

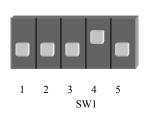

For Slot-0 operation, SW1, SW2, SW3, and STP7 should be configured as:

#### <u>SW1</u>

| Switch | Position |

|--------|----------|

| 1      | down     |

| 2      | down     |

| 3      | down     |

| 4      | up       |

| 5      | down     |

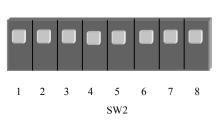

#### <u>SW2</u>

| Switch | Position |

|--------|----------|

| 1      | up       |

| 2      | up       |

| 3      | up       |

| 4      | up       |

| 5<br>6 | up       |

| 6      | up       |

| 7      | up       |

| 8      | up       |

#### <u>SW3</u>

| Switch | Position |

|--------|----------|

| 1      | left     |

| 2      | right    |

| 3      | left     |

| 4      | left     |

| 5      | left     |

| 6      | right    |

#### <u>STP7</u>

| Switch | Position |

|--------|----------|

| strap  | down     |

| SW3 |  |

|-----|--|

| 1   |  |

| 2   |  |

| 3   |  |

| 4   |  |

| 5   |  |

| 6   |  |

|     |  |

## **Selecting Non Slot-0 Operation**

For Non Slot-0 operation, SW1, SW3, and STP7 should be configured as:

#### <u>SW1</u>

| Switch |      |

|--------|------|

| 1      | up   |

| 2      | up   |

| 3      | up   |

| 4      | down |

| 5      | down |

<u>SW3</u>

| Switch | Position |

|--------|----------|

| 1      | left     |

| 2      | left     |

| 3      | right    |

| 4      | left     |

| 5      | right    |

| 6      | left     |

#### <u>STP7</u>

| Switch | Position |

|--------|----------|

| strap  | up       |

Note that the logical address switch (SW2) must be configured to a value *not* 0 (not all up).

## **Setting the Logical Address**

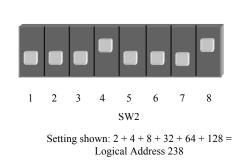

The Logical address of the V155 module is set via SW2. The individual switches of SW2 represent a binary combination of numbers in the range of 0 to 255. The switch settings are made by depressing each Logical Address switch to the desired location. A switch that is in the DOWN position yields a bit set to a one. A switch that is in the UP position yields a bit set to a zero. The left-most switch corresponds to Logical Address bit 128 and the right-most switch corresponds to Logical Address bit 1, as shown below:

#### <u>SW2</u>

| Switch | Weight   |

|--------|----------|

| 1      | 128      |

| 2      | 64<br>32 |

| 2 3    | 32       |

| 4      | 16       |

| 5 6    | 8        |

| 6      | 4        |

| 7      | 2        |

| 8      | 1        |

To statically assign a Logical Address to the V155, simply set the 8-position DIP switch to the desired Logical Address in the range of 0 through 254. This sets the Logical Address of the V155 and may only be altered by changing the setting on the DIP switch.

The V155 may also be Dynamically Configured. A device that is Dynamically Configured must have its Logical Address set to 255 ( $FF_{16}$ ). A device that is Dynamically Configured has its Logical Address set by the Resource Manager when the Logical Address Register of the V155 is written. Dynamic Configuration is used to avoid conflicts in setting up a device's Logical Address.

## Installation

#### **Module Installation**

After all the user selectable configuration parameters have been setup, the module may then be inserted into the VXI chassis. If the V155 is configured for Slot0 operation, insert the V155 into the left-most slot (Slot0) of the VXI chassis. For a non-Slot0 configuration, insert the V155 into any slot in the range of 1 through 13.

| CAUTION: | TURN OFF MAINFRAME POWER BEFORE INSERTING OR REMOVING A VXI <i>bus</i> MODULE. |

|----------|--------------------------------------------------------------------------------|

|          | REMEMBER TO REMOVE THE INTERRUPT ACKNOWLEDGE AND                               |

| WARNING: | BUS GRANT DAISY CHAIN JUMPERS BEFORE INSERTING A VXI<br>MODULE                 |

The VXI*bus* backplane must be properly configured before inserting a VXI module and applying power. The Interrupt Acknowledge jumper must be removed from the slot in which the VXI module is to be inserted. The Bus Grant jumpers must also be removed from the slot in which the VXI module is to be inserted. All unoccupied slot locations must have the Interrupt Acknowledge and Bus Grant jumpers installed so that the interrupt and grant continuity is not disrupted by any open slots. When using backplanes that auto-configure, these steps are not necessary since the installation of a VXI module in the chassis makes the required configuration occur.

#### **Operating System Installation**

Installation of the Operating System is performed exactly as if the V155 where an ordinary laptop or desktop system.

OS installation requires an external USB CD drive.

At this point in time, only Windows XP is supported.

#### **Software Installation**

The V155 can be operated as a VME-based controller by simply installing the included VMIC IO Works software and using their VMIC VMEbus Access API; the VMIC installation disk contains full on-line documentation.

The V155 can also be operated as a full VXI-based controller by purchasing the optional KineticSystems VISA & VISA VMIC Plug-in.

#### VMIC VMEbus Access

The VMIC VMEbus Access Software contains all the drivers and support files needed for VME access on the V155 SBC, and should be installed first. Insert the VMIC disk and run the appropriate setup.exe.

#### KineticSystems VISA Installation

If slot-0 VISA-level access is desired, KineticSystems VISA and the VISA VMIC Plug-in will need to be purchased separately and installed. Since the VISA VMIC Plug-in is built on top of the VMIC Access Software, the VMIC layer must always be installed even if no application program intends to directly access the VMIC API.

VISA is installed first. If KineticSystems VISA was already installed on the system as part of a previous KineticSystems product installation, this step is omitted. Insert the KineticSystems VISA disk and run the appropriate setup.exe.

The VISA VMIC Plug-in is installed last. Insert the KineticSystems VISA VMIC Plug-in disk and run the appropriate setup.exe.

#### **Directory Structure**

The V155 installation creates the directory structure shown below. Folders are represented by the  $(\rightarrow)$  symbol. Files are represented by the  $(\bullet)$  symbol.

#### →VXIPNP Root level (VPNPPATH)

→WINNT

$\rightarrow$  Bin

- pisadevimpvmicvxi.dll

- pisa.dll

- resman.exe

#### $\rightarrow$ Include

- pisavxi.h

- visa.h

- visatype.h

- vpptype.h

- $\rightarrow$  Lib

- $\rightarrow$  Cvi (appropriate for use in CVI compiler projects)

- visa32.lib

- $\rightarrow$  Msc (appropriate for use in Microsoft Visual C/C++ projects)

- visa32.lib

#### →WinNT/Windows (System Root)

#### $\rightarrow$ system32

• visa32.dll

#### VMIC Plug-in Resman options

The KineticSystems VISA *resman* utility accesses the VISA device manager to probe for hardware installed on the system.

The VMIC Plug-in adds 1 new option to resman:

• --vmicDelay <timeout>

This option specifies the number of seconds to wait after SYSRESET before probing for VXI modules controlled by a V155. By default, there is a 5 second delay between the deassertion of SYSRESET and probing for hardware devices; this period allows devices time to perform their reset and self test routines. This option changes the length of the delay. timeout is in seconds.

Please consult your KineticSystems VISA manual for more information on resman.

## Chapter3: VXI*bus* Configuration Registers and Operational Registers

The following table shows the various registers located in A16 space for the V155:

| A16 Offset       | Write Access                         | Read Access                  |

|------------------|--------------------------------------|------------------------------|

| 0016             | Logical Address Register             | Identification               |

| 0216             | Reserved                             | Device Type Register         |

| 0416             | Status/Control Register              | Status/Control Register      |

| 0616             | Reserved                             | Reserved                     |

| 0816             | MODID Register                       | MODID Register               |

| 0A <sub>16</sub> | Reserved                             | Reserved                     |

| 0C <sub>16</sub> | Reserved                             | Reserved                     |

| 0E <sub>16</sub> | Reserved                             | Reserved                     |

| 10 <sub>16</sub> | Reserved                             | Reserved                     |

| 12 <sub>16</sub> | Reserved                             | Reserved                     |

| 14 <sub>16</sub> | Reserved                             | Reserved                     |

| 16 <sub>16</sub> | Reserved                             | Reserved                     |

| 18 <sub>16</sub> | Reserved                             | Reserved                     |

| 1A <sub>16</sub> | Reserved                             | Reserved                     |

| $1C_{16}$        | Reserved                             | Reserved                     |

| $1E_{16}$        | Reserved                             | Reserved                     |

| 2016             | Reserved                             | Suffix High Register         |

| 22 <sub>16</sub> | Reserved                             | Suffix Low Register          |

| 24 <sub>16</sub> | Reserved                             | Serial Number High Register  |

| 2616             | Reserved                             | Serial Number Low Register   |

| 2816             | Reserved                             | Reserved                     |

| 2A <sub>16</sub> | Reserved                             | Interrupt Status Register    |

| 2C <sub>16</sub> | Interrupt Control Register           | Interrupt Control Register   |

| 2E <sub>16</sub> | Trigger Interrupt Mask               | Trigger Interrupt Source     |

| 30 <sub>16</sub> | Trigger Interrupt Source Clear       | Reserved                     |

| 32 <sub>16</sub> | Trigger Source Register              | Reserved                     |

| 34 <sub>16</sub> | Trigger Timer Configuration Register | Reserved                     |

| 3616             | Reserved                             | Reserved                     |

| 3816             | SBC Slave Mode Configuration         | Interrupt Status ID Register |

| 3A <sub>16</sub> | Reserved                             | Reserved                     |

| 3C <sub>6</sub>  | Miscellaneous Control Register       | Reserved                     |

## **ID/Logical Address Register**

The ID/Logical Address Register is a write/read register located at an offset of 00<sub>16</sub> from the A16 Logical Base Address. A read operation to this register returns the Device Class, the addressing modes of the device's operational registers and the Manufacturers' Identification. A write operation to this register address is typically executed by the Resource Manager during a Dynamic Configuration allocation sequence. During the sequence, the Resource Manager allocates a Logical Address to the V155 by writing a logical address value to the least significant eight bits of this register. The format and bit assignments of this register are shown in the following diagram. Since this register has write-only and read-only bits, two bit patterns are shown.

On read transactions:

|           |            |               |    |                 |    |    |   |   |   |   |   |   | - |   | 001 | 1 |

|-----------|------------|---------------|----|-----------------|----|----|---|---|---|---|---|---|---|---|-----|---|

|           | 15         | 14            | 13 | 12              | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

| Read-only | 1          | 1             | 1  | 1               | 1  | 1  | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0   | 1 |

|           | Cla<br>Reg | ss =<br>ister |    | essing<br>= A16 |    |    |   |   |   |   |   |   |   |   |     |   |

```

based

```

KineticSystems' Manufacturer ID = F29<sub>16</sub> (3881)

Bit(s) Mnemonic

#### Meaning

15:14 **Device Class** These bits are set to reflect the Device Class of the V155. This bit combination indicates that the V155 is a Register based Device. These bits are set to reflect the addressing mode(s) of the V155's 13:12 Address Space operational registers. Since all the communication registers of the V155 appear in A16 address space, the bits in this field are both set to one. Manufacturer This field reflects the manufacturer of a VXI device. This value is 11:0 3881(F29<sub>16</sub>) for KineticSystems.

On write transactions:

|            |    |          |    |    |    |    |   |   |   |   |   |         |         |   | 00 | h |

|------------|----|----------|----|----|----|----|---|---|---|---|---|---------|---------|---|----|---|

|            | 15 | 14       | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4       | 3       | 2 | 1  | 0 |

| Write-only |    | Not Used |    |    |    |    |   |   |   |   |   | Logical | Address | 5 |    |   |

| <b>Bit(s)</b> | <b>Mnemonic</b> | <b>Meaning</b>                                                                                                                                                                                                                                                                            |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8          | Not Used        | These 8 bits are not used. A write operation to these bits has no effect on the V155.                                                                                                                                                                                                     |

| 7:0           | 128-LA1         | Logical Address 128 through 1 are write-only bits used to set the V155's Logical Address during a Dynamic Configuration cycle executed by the Resource Manager. A Dynamic Configuration sequence is performed on a VXI module when its logical address has been set to 255 ( $FF_{16}$ ). |

02h

## **Device Type Register**

The Device Type Register is a read-only register located at an offset of  $02_{16}$  from the A16 Logical Base Address of the V155. This register contains the Model Code of the V155. Since the V155 is an A16-only device, the entire 16-bits of this field is used for the Model Code.

Model Codes for VXI Slot0 devices must be in the range of  $00_{16}$  to FF<sub>16</sub>. Model Codes for non-Slot0 devices must be in the range of  $100_{16}$  to FFFF<sub>16</sub>. When the V155 is configured for non-Slot0 operation, the Model Code returned in this register is  $155_{16}$ . When the V155 is configured for Slot0 operation, the  $100_{16}$  bit is set to zero, yielding a Model Code of  $55_{16}$ .

V155 Model Codes:

155<sub>16</sub> for non-Slot0 configurations 55<sub>16</sub> for Slot0 configurations

The following diagram shows the bit pattern for the Device Type Register for both Slot0 and non-Slot0 configurations.

For Slot0 Configurations:

|           |    |    |    |    |    |    |   |   |   |   |   |   |   | 04 |   |   |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|----|---|---|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

| Read-only | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1  | 0 | 1 |

For non-Slot0 Configurations:

|           |    |    | -  |    |    |    |   |   |   |   |   |   |   | 02h |   |   |  |  |  |  |  |  |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|---|---|--|--|--|--|--|--|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |  |  |  |  |  |  |

| Read-only | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1   | 0 | 1 |  |  |  |  |  |  |

## Status/Control Register

The Status/Control Register is a write/read register located at an offset of  $04_{16}$  from the A16 Logical Base Address of the V155. This register contains write-only, read-only and write/read bits. This register is used to monitor the Module ID VXI signal, control the assertion of SYSFAIL, control Soft Reset, and check the status of the Power-On Self Test. The following two diagrams show the Status/Control Register, one for read accesses and one for write.

|            | ID*       Meaning         Mnemonic       Meaning         Not Used       This bit is not used and read as a zero.         MODID*       This bit is set to a one if the module is not selected with |                                                                                                                                                                   |    |                                                                                                                                                                                                                                                |                                                                                                                            |        |       |        |        |       |     |   |     |      | 04] | h   |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|--------|-------|-----|---|-----|------|-----|-----|--|

|            | 15                                                                                                                                                                                                | 14                                                                                                                                                                | 13 | 12                                                                                                                                                                                                                                             | 11                                                                                                                         | 10     | 9     | 8      | 7      | 6     | 5   | 4 | 3   | 2    | 1   | 0   |  |

| Read-Write | 0                                                                                                                                                                                                 | MOD                                                                                                                                                               | 1  | 1                                                                                                                                                                                                                                              | 1                                                                                                                          | 1      | 1     | 1      | 1      | 1     | 1   | 1 | RDY | PASS | SYS | SFT |  |

|            |                                                                                                                                                                                                   | ID*                                                                                                                                                               |    | -                                                                                                                                                                                                                                              | -                                                                                                                          | -      | -     | -      | -      | -     | -   | - |     |      | INH | RST |  |

| Bit(s)     | Mn                                                                                                                                                                                                | emoni                                                                                                                                                             | ic |                                                                                                                                                                                                                                                |                                                                                                                            |        |       |        |        | Mean  | ing |   |     |      |     |     |  |

| 15         | Not                                                                                                                                                                                               | Used                                                                                                                                                              |    | This b                                                                                                                                                                                                                                         | oit is r                                                                                                                   | not us | ed an | d read | l as a | zero. |     |   |     |      |     |     |  |

| 14         | МО                                                                                                                                                                                                | on the VXI P2 connector. A zero indicates that the module is selected by the MODID signal.                                                                        |    |                                                                                                                                                                                                                                                |                                                                                                                            |        |       |        |        |       |     |   |     |      |     |     |  |

| 13:4       | Not                                                                                                                                                                                               | Used                                                                                                                                                              |    |                                                                                                                                                                                                                                                |                                                                                                                            |        |       |        |        |       |     |   |     |      |     |     |  |

| 3          | RD                                                                                                                                                                                                | Y                                                                                                                                                                 |    | These bits are not used and read as ones.<br>Ready is a read-only bit that is set to a one indicating successful completion of register initialization.                                                                                        |                                                                                                                            |        |       |        |        |       |     |   |     |      |     |     |  |

| 2          | PAS                                                                                                                                                                                               | PASS Pass is a read-only bit that is set to a one when the V155 has completed its power-on self-test without any errors. If an error occurs, this bit is set to a |    |                                                                                                                                                                                                                                                |                                                                                                                            |        |       |        |        |       |     |   |     |      |     |     |  |

| 1          | SYS                                                                                                                                                                                               | S INH                                                                                                                                                             |    |                                                                                                                                                                                                                                                | zero and the SYSFAIL signal is asserted by the V155.<br>SYSFAIL INHIBIT. Reading this bit as a one indicates that the V155 |        |       |        |        |       |     |   |     |      |     |     |  |

| 0          | SFT                                                                                                                                                                                               | RST                                                                                                                                                               |    | prevented from driving the backplane SYSFAIL line.<br>SFT RST This bit is read as a one when the V155 has been placed into the Soft Reset state. Writing this register with this bit set to a zero removes the V155 from the soft reset state. |                                                                                                                            |        |       |        |        |       |     |   |     |      |     |     |  |

For read operations executed to the Status/Control Register:

|                       |     |                       |    |                                                                                                                                                                                                      |        |        |        |         |   |                       |   |   |   |   | 04] | h   |  |

|-----------------------|-----|-----------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|---------|---|-----------------------|---|---|---|---|-----|-----|--|

|                       | 15  | 14                    | 13 | 12                                                                                                                                                                                                   | 11     | 10     | 9      | 8       | 7 | 6                     | 5 | 4 | 3 | 2 | 1   | 0   |  |

| Write-only            |     |                       |    |                                                                                                                                                                                                      |        |        | Not    | Used    |   |                       |   |   |   |   | SYS | SFT |  |

| write-only            |     |                       |    |                                                                                                                                                                                                      |        |        | NOU    | USEU    |   |                       |   |   |   |   | INH | RST |  |

| <b>Bit(s)</b><br>15:2 | -   | e <b>moni</b><br>Used | c  | These                                                                                                                                                                                                | e bits | are no | t used | d for v |   | <b>Mean</b><br>operat | 0 |   |   |   |     |     |  |

| 1                     | SYS | INH                   |    | SYSFAIL INHIBIT is a write/read bit used to inhibit the V155 from asserting the backplane signal SYSFAIL. Setting this bit to a one disables the assertion of SYSFAIL and a zero enables the signal. |        |        |        |         |   |                       |   |   |   |   |     |     |  |

| 0                     | SFT | RST                   |    | a one                                                                                                                                                                                                |        |        |        |         |   |                       |   |   |   |   |     |     |  |

For write operations executed to the Status/Control Register:

## **MODID Register**

The MODID Register is a read/write register located at an offset of  $08_{16}$  from the A16 Logical Base Address of the V155. This register is only available when the V155 is configured as a Slot0 device. When the V155 is configured for non-Slot0 operation, the MODID Register is reserved.

The MODID Register is a write/read register used to control the MODID geographic addressing lines on the VXI P2 connector. Each of the 13 slots in the VXI chassis has an individual line that can be asserted and monitored through the MODID Register. Before any MODID lines can be asserted by the V155, the Output Enable bit (bit 13) of the register must be set to a one. When the outputs are enabled, setting a MODID bit location to a one asserts the associated MODID signal.

The data read from the MODID bits in this register do not necessarily reflect the state of the bits that were written to this register. Instead, a read of this register returns the actual state of each MODID line.

The following diagram shows the bit pattern for the MODID Register.

|            |    |    |        |    |     |     |     |     |     |     |     |     |     |     | <b>08</b> | h   |   |

|------------|----|----|--------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------|-----|---|

|            | 15 | 14 | 13     | 12 | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1         | 0   | ł |

| Read-Write | 1  | 1  | MODID  |    | MID       | MID |   |

|            |    |    | Enable | 12 | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1         | 0   |   |

| Bit(s) | Mnemonic        | Meaning                                                                                                                                                                                                 |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:14  | Not Used        | This bit is not used and read as a ones.                                                                                                                                                                |

| 13     | MODID<br>Enable | OUTPUT ENABLE is a write/read bit used to enable or disable the V155 from driving the MODID signals. Setting this bit to a one enables the drivers and a zero disables them.                            |

| 12:0   | MID 12-0        | MODULE ID 12 through 0 are write/read bits used to assert and monitor<br>the MODID signals. Writing a bit with a one will assert (as indicated by a<br>high state) the corresponding slot's MODID line. |

## Suffix High Register

The Suffix High Register is a read-only register located at an offset of  $20_{16}$  from the A16 Logical Base Address of the V155. This register is used in combination with the Suffix Low Register to determine the module model number suffix. The Suffix High Register contains the first two ASCII characters of the suffix and the Suffix Low Register contains the last two characters. The suffix shown is for the V155-AA11 module.

The bit pattern for the Suffix High Register is as follows:

|           |    |    |    |    |    |    |   |   |   |   |   |   |   | 20h |   |   |  |  |  |  |  |  |  |  |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|---|---|--|--|--|--|--|--|--|--|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |  |  |  |  |  |  |  |  |

| Read-only | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0   | 0 | 1 |  |  |  |  |  |  |  |  |

....

## **Suffix Low Register**

The Module Suffix Low Register is a read-only register located at an offset of  $22_{16}$  from the A16 Logical Base Address of the V155. This register is used in combination with the Suffix High Register to determine the module model number suffix. The Suffix Low Register contains the last two ASCII characters of the suffix and the Suffix High Register contains the first two characters. The suffix shown is for the V155-AA11 module.

The bit pattern for the Suffix Low Register is as follows:

|           |    |    |    |    |    |    |   |   |   |   |   |   |   |   | 22 | h |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|----|---|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

| Read-only | 0  | 0  | 1  | 1  | 0  | 0  | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0  | 1 |

## Serial Number High Register

The Serial Number High Register is a read-only register located at an offset of  $24_{16}$  from the A16 Logical Base Address of the V155. This register is used in conjunction with the Serial Number Low Register to define the serial number of the V155. The following diagram shows the bit pattern of the Serial Number High Register.

|            |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 24 | h  |

|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|            | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Devel Only | SN |

| Read-Only  | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

## **Serial Number Low Register**

The Serial Number Low Register is a read-only register located at an offset of 26<sub>16</sub> from the A16 Logical Base Address of the V155. This register is used in conjunction with the Serial Number High Register to define the serial number of the V155. The following diagram shows the bit pattern of the Serial Number Low Register.

|           |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 26 | h  |

|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Baad Only | SN |

| Read-Only | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

## Interrupt Status Register

The Interrupt Status Register is a read-only register located at an offset of 2A<sub>16</sub> from the A16 Logical Base Address of the V155. The contents of this register are enabled onto the VME*bus* during an interrupt acknowledge cycle. This register contains the Logical Address of the V155 in the lower 8-bits of the register and the upper 8-bits contains the cause/status of the interrupt. The lower 8-bits of this register return the Logical Address of the V155 only for interrupt acknowledges cycles. An I/O read of this field returns all 8-bits set to ones.

The V155 has two interrupt sources. One of the sources is from a pre-selected VXI Trigger input and the other source is from Location Monitors. The VXI interrupt sources are enabled through the Trigger Interrupt Mask Register located at offset  $2E_{16}$ . The Location Monitor interrupt sources are enabled through the Location Monitor Interrupt Control Register located at an offset of  $3A_{16}$ . These two registers must be appropriately enabled before the V155 can generate an interrupt source. The interrupt source(s) may then generate a VXI interrupt request when interrupts are enabled in the Interrupt Control Register located at an offset of  $2C_{16}$ .

The interrupt acknowledge cycle executed by the Interrupt Handler reads a 16-bit value from the V155. The lower 8-bits of this data reflects the Logical Address of the device generating the interrupt. The upper 8-bits reflects the cause of the interrupt. Of the upper 8-bits, only 2 of them are used by the V155. Once an interrupt acknowledges cycle occurs, the interrupt source bits that were set in this register when the interrupt vector was read are reset to zero. This will also occur when the Interrupt Status Register is read.

The format of the Interrupt Status Register is as follows:

| 2A        | h  |       |      |    |                             |                                |                                    |                            |                                   |                                                  |                           |                          |                          |                           |                           |                       |                     |

|-----------|----|-------|------|----|-----------------------------|--------------------------------|------------------------------------|----------------------------|-----------------------------------|--------------------------------------------------|---------------------------|--------------------------|--------------------------|---------------------------|---------------------------|-----------------------|---------------------|

|           | 15 | 14    | 13   | 12 | 11                          | 10                             | 9                                  | 8                          | 7                                 | 6                                                | 5                         | 4                        | 3                        | 2                         | 1                         | 0                     |                     |

| Read-Only | 0  | 0     | 0    | 0  | 0                           | 0                              | LOC                                | TRG                        | LA                                | LA                                               | LA                        | LA                       | LA                       | LA                        | LA                        | LA                    |                     |

|           |    |       |      |    |                             |                                | MON                                | IN                         | 128                               | 64                                               | 32                        | 16                       | 8                        | 4                         | 2                         | 1                     | J                   |

| Bit(s)    |    |       | moni | C  |                             |                                |                                    | Mear                       |                                   |                                                  |                           |                          |                          |                           |                           |                       |                     |

| 15:10     |    | Not I | Jsed |    | The                         | se bit                         | s are                              | not us                     | ed an                             | d read                                           | d as ze                   | eros.                    |                          |                           |                           |                       |                     |

| 9         |    | LOC   | MON  | 1  | clea<br>the<br>Inte<br>loca | r bit<br>Loca<br>rrupt<br>tion | that is<br>tion M<br>Cont<br>monit | s set v<br>Monit<br>rol R  | vhen<br>or Int<br>egiste<br>errup | INT<br>an int<br>terrup<br>er. T<br>t, the<br>d. | errup<br>ts ena<br>'o fin | t sour<br>abled<br>d out | rce is<br>in th<br>the   | gener<br>e Loc<br>actual  | ated l<br>cation          | by on<br>Mon<br>se of | e of<br>itor<br>the |

| 8         |    | TRG   | IN   |    | set<br>trigg<br>Reg         | when<br>ger i<br>jister.       | an i<br>nput<br>To f               | nterru<br>interr<br>ind ou | pt so<br>rupt so<br>ut the        | PT SC<br>urce i<br>source<br>actua<br>ce Re      | is ger<br>es in<br>l caus | the<br>the<br>se of t    | d by<br>Trigg<br>the tri | one o<br>ger Ii<br>gger i | of the<br>nterru<br>input | e enat<br>pt M        | oled<br>Iask        |

| 7:0       |    | LA12  | 28:1 |    | the                         | V155                           | duri                               | ng an                      | inter                             | 28 thro<br>rupt a<br>rn all                      | cknov                     |                          |                          | •                         |                           |                       |                     |

## Interrupt Control Register

The Interrupt Control Register is a write/read register located at an offset  $2C_{16}$  from the A16 Logical Base Address of the V155. This register is used to configure the V155 for interrupt sourcing. The Interrupt Request Level, Interrupt Enable, and Interrupt Source Mask are contained in this register.

The format and description of the Interrupt Control Register are shown in the following diagram.

|                        |    |                      |     |    |                           |                          |                                  |                                |                         |                           |                          |                           |                         |                                             | 20                        | <sup>c</sup> h          |               |

|------------------------|----|----------------------|-----|----|---------------------------|--------------------------|----------------------------------|--------------------------------|-------------------------|---------------------------|--------------------------|---------------------------|-------------------------|---------------------------------------------|---------------------------|-------------------------|---------------|

|                        | 15 | 14                   | 13  | 12 | 11                        | 10                       | 9                                | 8                              | 7                       | 6                         | 5                        | 4                         | 3                       | 2                                           | 1                         | 0                       | ł             |

| Read-Write             | 1  | 1                    | 1   | 1  | 1                         | 1                        | LOC<br>MON*                      | TRG<br>IN*                     | IR<br>ENA*              | 1                         | IRQ<br>S3                | IRQ<br>S2                 | IRQ<br>S1               | 1                                           | 1                         | 1                       |               |

| <b>Bit(s)</b><br>15:10 |    | <b>Mnen</b><br>Not U |     |    | The                       | se bit                   |                                  | <b>Mea</b><br>not us           | ning<br>sed an          | d read                    | d as o                   | nes.                      |                         |                                             |                           |                         |               |

| 9                      |    | LOC                  | MON | *  | used<br>one<br>Loc<br>one | d to e<br>of th<br>ation | nable<br>ne Lo<br>Mon<br>oles th | and of and of a cation itor In | disabl<br>Mor<br>nterru | e the<br>nitor i<br>pt Co | gene<br>interro<br>ntrol | ration<br>upt so<br>Regis | of a<br>ources<br>ster. | LE is a<br>VXI<br>s are<br>Settir<br>d a ze | interr<br>enabl<br>1g thi | upt w<br>ed in<br>s bit | then the to a |

| 8                      |    | TRG ]                | IN* |    | enal<br>the<br>gen        | ble ar<br>enab<br>eratec | nd dis<br>led in<br>l. Se        | able 1<br>nterru<br>tting      | the ge<br>pt so         | enerat<br>urces<br>bit to | ion o<br>in t            | f a V<br>he Ti            | XI in<br>tigger         | rite/re<br>terrup<br>Inte<br>the in         | t whe<br>rrupt            | en on<br>Masi           | e of<br>k is  |

| 7                      |    | IR EN                | IA* |    | enal<br>VM<br>gen         | ble/di<br>E <i>bus</i>   | sable<br>. Se                    | the V<br>etting                | 155 f<br>this           | rom g<br>bit t            | genera<br>o a            | ating a<br>one            | an int<br>disabl        | te/rea<br>errupt<br>es th<br>nables         | t requ<br>e Vl            | est to<br>55 f          | the trom      |

| 6                      |    | Not U                | sed |    | Thi                       | s bit i                  | s not                            | used a                         | and re                  | ad as                     | a one                    |                           |                         |                                             |                           |                         |               |

| 5:3                    |    | IRQS:                | 3:1 |    | used                      | d to                     | select                           | the                            |                         | ed int                    | errup                    |                           | •                       | l are<br>evel                               |                           |                         |               |

| IRQ S3 | IRQ S2 | IRQ S1 | Interrupt Request Level |

|--------|--------|--------|-------------------------|

| 0      | 0      | 0      | IRQ7                    |

| 0      | 0      | 1      | IRQ6                    |

| 0      | 1      | 0      | IRQ5                    |

| 0      | 1      | 1      | IRQ4                    |

| 1      | 0      | 0      | IRQ3                    |

| 1      | 0      | 1      | IRQ2                    |

| 1      | 1      | 0      | IRQ1                    |

| 1      | 1      | 1      | Disconnected            |

The following chart shows the interrupt request level selections.

2:0

Not Used

These bits are not used and read as ones.

2Eh

## **Trigger Interrupt Mask/Trigger Interrupt Source Register**

The Trigger Interrupt Mask/Trigger Interrupt Source Register is located at an offset of  $2E_{16}$  from the A16 Logical Base Address of the V155. This register serves two purposes, depending on the direction of the transfer. A write operation to this register address accesses the Trigger Interrupt Mask Register. This register is used to enable and disable interrupts to the VXI bus on the occurrence of a trigger condition. Trigger conditions include the 8 VXI TTL Trigger lines and the two ECL VXI Trigger lines. A mask bit is set to a one to enable the interrupt source and set to a zero to disable the source.

The second register at this address is the Trigger Interrupt Source Register. This read-only register is used to determine which trigger event caused the interrupt source. Each bit read as a one was involved in generating the trigger interrupt source. After an interrupt has been generated and acknowledged, the Trigger Interrupt Source Clear Register must be written with data to clear the individual interrupt source.

The following two diagrams show the two registers.

|                        | 15 | 14           | 13                    | 12   | 11          | 10               | 9               | 8            | 7           | 6             | 5                         | 4    | 3              | 2     | 1      | 0                        |     |

|------------------------|----|--------------|-----------------------|------|-------------|------------------|-----------------|--------------|-------------|---------------|---------------------------|------|----------------|-------|--------|--------------------------|-----|

| Write-Only             |    |              | Not I                 | lood |             |                  | ECL             | ECL          | TTL         | TTL           | TTL                       | TTL  | TTL            | TTL   | TTL    | TTL                      |     |

| write-Only             |    |              | NOL                   | Jseu |             |                  | TG1             | TG0          | TG7         | TG6           | TG5                       | TG4  | TG3            | TG2   | TG1    | TG0                      |     |

| <b>Bit(s)</b><br>15:10 |    | Mne<br>Not U | <b>moni</b> o<br>Used | C    |             |                  | ts are<br>the V |              | sed ai      |               | l <b>eanir</b><br>ting tl | 0    | o one          | s doe | s not  | have                     | any |

| 9:8                    |    | ECL          | TG1:                  | 0    | gen<br>Trig | eratio<br>gger 1 | n of            | a VX<br>asse | I interted. | rrupt<br>A bi | wher<br>it set            | to a | corre<br>one e | spond | ing V  | nable<br>/XI E<br>interr | ECL |

| 7:0                    |    | TTL          | TG1:                  | 0    | gen<br>Trig | eratio<br>gger 1 | n of            | a VX<br>asse | I interted. | rrupt<br>A bi | wher<br>it set            | to a | corre<br>one e | spond | ling V | nable<br>/XI T<br>interr | TL  |

Trigger Interrupt Mask Register (Write-Only):

| Trigger | Interrupt Sou | urce Register ( | Read-only): |

|---------|---------------|-----------------|-------------|

|---------|---------------|-----------------|-------------|

|                        |                      | pt 00 |     | iteg |                     | (1.004)                  | a orn.                   | ,,.                  |                         |                         |                                              |                          |                         |                           | <b>2</b> E      | h             |            |

|------------------------|----------------------|-------|-----|------|---------------------|--------------------------|--------------------------|----------------------|-------------------------|-------------------------|----------------------------------------------|--------------------------|-------------------------|---------------------------|-----------------|---------------|------------|

|                        | 15                   | 14    | 13  | 12   | 11                  | 10                       | 9                        | 8                    | 7                       | 6                       | 5                                            | 4                        | 3                       | 2                         | 1               | 0             |            |

| Read-Only              |                      |       | Not | Used |                     |                          | ECL                      | ECL                  | TTL                     | TTL                     | TTL                                          | TTL                      | TTL                     | TTL                       | TTL             | TTL           |            |

| Read-Only              |                      |       | Not | 0360 |                     |                          | TG1                      | TG0                  | TG7                     | TG6                     | TG5                                          | TG4                      | TG3                     | TG2                       | TG1             | TG0           | ļ          |

| <b>Bit(s)</b><br>15:10 | <b>Mner</b><br>Not U |       | e   |      | The                 | se bit                   | s are :                  | not us               | sed an                  |                         | leanir<br>d as z                             | 0                        |                         |                           |                 |               |            |

| 9:8                    | ECL                  | TG1:0 | 0   |      | reac<br>corr<br>was | l as a<br>respor<br>enat | a one<br>nding<br>oled.  | when<br>VXI<br>Read  | n the<br>ECL<br>ling t  | V15<br>Trig<br>his b    | 1 an<br>5 has<br>ger li<br>it as<br>n inter  | rece<br>ne an<br>a zer   | ived the o ind          | the as<br>Inter<br>icates | ssertic<br>rupt | on of<br>Mask | the<br>bit |

| 7:0                    | TTL '                | TG7:( | 0   |      | are<br>corr<br>was  | read<br>espor<br>enat    | as a c<br>nding<br>pled. | one w<br>VXI<br>Read | hen tl<br>TTL<br>ling t | he V1<br>Trigg<br>his b | 7 thr<br>55 ha<br>ger li<br>it as<br>n inter | as rec<br>ne an<br>a zer | eived<br>d the<br>o ind | the a<br>Inter<br>icates  | sserti<br>rupt  | on of<br>Mask | the bit    |

## **Trigger Interrupt Source Clear Register**

The Trigger Interrupt Source Clear Register is a write-only register located at an offset of  $30_{16}$  from the A16 Logical base Address of the V155. This register is used to clear the Interrupt Source bits in the Trigger Interrupt Source Register once they have been set by the receipt of a preselected trigger input. Any bit location set to a one when writing to this register clears the corresponding Interrupt Source bit. Any bit set to a zero has not effect on the Interrupt Source.

The following diagram shows the bit layout for the Trigger Interrupt Source Clear Register.

|                        |     |                |       |      |      |       |                         |       |       |      |       |       |       |        | 30     | h    |      |

|------------------------|-----|----------------|-------|------|------|-------|-------------------------|-------|-------|------|-------|-------|-------|--------|--------|------|------|

|                        | 15  | 14             | 13    | 12   | 11   | 10    | 9                       | 8     | 7     | 6    | 5     | 4     | 3     | 2      | 1      | 0    |      |

| Write-Only             |     |                | Not l | lead |      |       | ECL                     | ECL   | TTL   | TTL  | TTL   | TTL   | TTL   | TTL    | TTL    | TTL  |      |

| write-Only             |     |                | NOL   | Useu |      |       | TG1                     | TG0   | TG7   | TG6  | TG5   | TG4   | TG3   | TG2    | TG1    | TG0  |      |

| <b>Bit(s)</b><br>15:10 |     | emor<br>t Usec | -     |      |      |       | ts are<br>the V         |       | 0     | Any  | write | to th | ese b | it loc | ations | have | e no |

| 9:8                    | EC  | L TG           | 1:0   |      | writ | e-onl | ECL<br>y bit<br>sourc   | s use | ed to | clea | r the | cor   | respo | nding  | ECI    |      |      |

| 7:0                    | TT] | L TGʻ          | 7:0   |      | writ | e-onl | TTL '<br>y bit<br>sourc | s use | ed to | clea | r the | e cor | respo | nding  | TTI    | 0    |      |

## **Trigger Source Register**

The Trigger Source Register is a write-only register located at an offset of  $32_{16}$  from the A16 Logical Base Address of the V155. This register is used to source the VXI ECL and VXI TTL. This register allows the trigger signals to be either asserted, negated or pulsed. The binary combination of bits 15 and 14 of this register determine what action is to be taken on the selected trigger signals. The following chart shows the binary combination of the control bits and the effect they have on the selected trigger signals.

| CNTL1 | <b>CNTL0</b> | Effect On Trigger Signal |

|-------|--------------|--------------------------|

| 0     | 0            | Assertion                |

| 0     | 1            | Negation                 |

| 1     | 0            | Pulse                    |

| 1     | 1            | Reserved                 |

When a trigger is asserted through the Trigger Source Register, it remains asserted until either a reset condition occurs or the Trigger Source Register is written to negate the trigger signal. A pulsed output lasts for approximately 1.5 microseconds.

|              |       | 0            |       |     |                   | •                                 |                  |                           |                          | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |                         |                            |                           | 32h                        |                                                    |

|--------------|-------|--------------|-------|-----|-------------------|-----------------------------------|------------------|---------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------|----------------------------|---------------------------|----------------------------|----------------------------------------------------|

|              | 15    | 14           | 13    | 12  | 11                | 10                                | 9                | 8                         | 7                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                         | 4                       | 3                          | 2                         | 1                          | 0                                                  |