## Model V200

16 or 32-Channel Sigma-Delta ADC

## Instruction Manual

January 30, 2001

© 1997, 1998, 1999, 2000, 2001 Copyright by KineticSystems Company, LLC Lockport, Illinois All Rights Reserved

## Contents

| Getting Startedi                                         |

|----------------------------------------------------------|

| How to Use This Manuali<br>Terminologyi<br>Conventionsii |

| Chapter I: Introduction1                                 |

| General Description                                      |

| Chapter II: Unpacking and Installation7                  |

| Configuration                                            |

| Chapter III: Programming Information17                   |

| VXI <i>bus</i> Addressing                                |

| ADC Clock Source Select                                  |

| Appendix A: Example Setup Procedures                     |

| Group A No Limit Checking Example                        |

| Appendix B: Connector Pinouts                            |

| Appendix C: Register Maps102                             |

| Configuration Registers, A16 Space                       |

| Appendix D: Switch and Strap Locations                   |

| Index106                                                 |

## Tables

| Table              | 1 DSP Status Codes                                                    | 70  |

|--------------------|-----------------------------------------------------------------------|-----|

| Table 2            | 2 Input Path Selections                                               | 73  |

| Table 3            | 3 Gain Selections                                                     | 73  |

| Table 4            | 4 Clock Modes                                                         | 75  |

| Table #            | 5 Oversample Clock Divisors                                           | 76  |

| Table              | 6 External Sample Clock Range                                         | 76  |

| Table <sup>·</sup> | 7 Calibration Register Values, Internal Source                        | 81  |

| Table 8            | 8 Threshold/Slope Limit Checking Exceptions when sample rate > 100kHz | 83  |

| Table 9            | 9 Minimum/Maximum Limit Checking Exceptions when sample rate > 100kHz | 83  |

| Table 1            | 0 50 Pin High Density Connector: P4 Pinout                            | 97  |

| Table 1            | 1 50 Socket High Density Connector: P3 Pinout for 16 Channel V200     | 98  |

| Table 1            | 2 50 Pin High Density Connector: P3 Pinout for 32 Channel V200        | 99  |

|                    | 3 VXIbus P1 Connector                                                 |     |

| Table 1            | 4 VXIbus P2 Connector                                                 | 101 |

## Figures

| FIGURE | 1 - V200 Main Card                                 | 1  |

|--------|----------------------------------------------------|----|

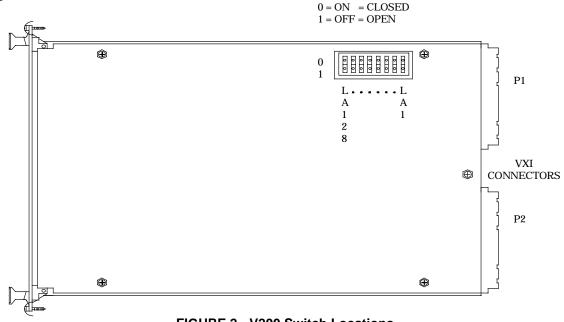

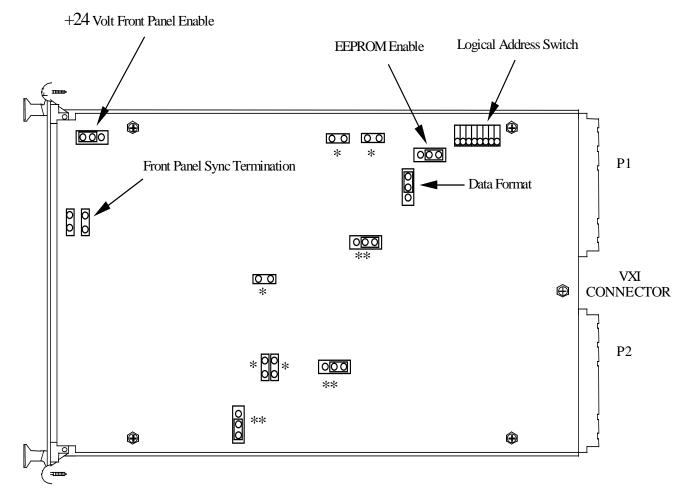

| FIGURE | 2 - V200 Switch Locations                          | 7  |

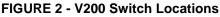

| FIGURE | 3 - Logical Address Switches                       | 8  |

| FIGURE | 4 - V200 Strap Locations                           | 8  |

| FIGURE | 5 - V200 +24 Volt Strap Location                   | 9  |

| FIGURE | 6 - V200 Motorola/Intel Data Format Strap Location | 10 |

| FIGURE | 7 - V200 Upgrade Locations                         | 11 |

| FIGURE | 8 - V200 Front Panel                               | 14 |

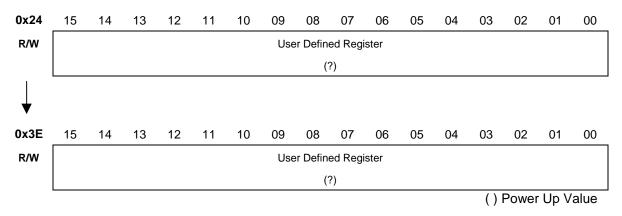

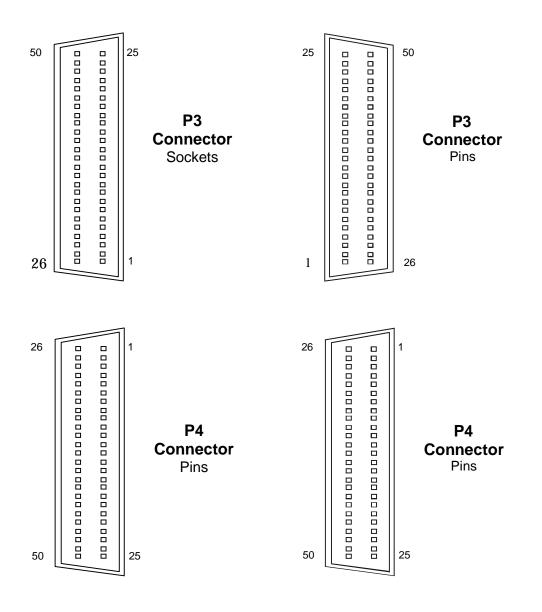

| FIGURE | 9 - 50 Pin High Density Connector P3 and P4        | 96 |

|        | 10 - V200 Switch and Strap Locations               |    |

|        |                                                    |    |

Data Sheet

# **Getting Started**

## How to Use This Manual

This manual is organized into four chapters:

- The *Introduction* chapter describes the capabilities of the V200 and how it can be used in a wide variety of applications.

- The *Unpacking and Installation* chapter explains how to install the V200 into a VXI chassis. In addition, a procedure for installing field upgrades for the V200 is also provided.

- The *Programming Information* chapter explains how to access and control the V200. The first half of the section explains the use of the Configuration Registers. These general purpose registers are standard registers defined by the VXI standard which is used to identify the module and control interrupts. The second half of the section explains the use of the Operational Registers. The registers are specific for operation and control of the V200.

- The *Appendices* provide additional information that may be helpful in the use of the V200. Topics include register layout, module calibration procedures, grounding techniques when connecting field wiring, and programming examples.

## Terminology

| Term                       | Description                                                                                                                                                                                                                                                                                                                  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A16 Space                  | As described in the VXI specification, this mnemonic is used to describe<br>the first 64 kBytes of address space. Every VXI module is<br>automatically allocated a 64-byte block of this address space (also<br>known as Configuration Registers). The exact location is determined<br>by the logical address of the module. |

| A32 Space                  | As described in the VXI specification, this mnemonic is used to describe<br>the 4 Giga-byte block of address space provided. Any module can<br>request a block of this address space from information contained in its<br>Configuration Registers. This memory block is also called the<br>Operational Registers.            |

| Configuration<br>Registers | See A16 Space.                                                                                                                                                                                                                                                                                                               |

The following is a list of some of the terms used throughout this manual:

| D16                      | As described in the VXI specification, this mnemonic is used to describe a single 16-bit data transfer.                                                                                                                                                                                                                                                                                                               |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D16 BLK                  | As described in the VXI specification, this mnemonic is used to describe a 16-bit block transfer.                                                                                                                                                                                                                                                                                                                     |

| D32                      | As described in the VXI specification, this mnemonic is used to describe<br>a single 32-bit data transfer. This mode is not supported by all Slot-0<br>controllers. Check the owners manual for the Slot-0 before attempting<br>this type of transfer.                                                                                                                                                                |

| D32 BLK                  | As described in the VXI specification, this mnemonic is used to describe<br>a 32-bit block transfer. This is the fastest transfer type supported by<br>the V200. This mode is most beneficial when retrieving data from the<br>ADC (i.e., through Ping/Pong). However, this mode may not be<br>supported by the Slot-0 controller. Check the owners manual for the<br>Slot-0 before attempting this type of transfer. |

| Logical<br>Address       | Every VXI module is given a unique logical address. There are a total of 256 logical addresses with 0 reserved for the Slot-0 controller.                                                                                                                                                                                                                                                                             |

| Operational<br>Registers | See A32 Space.                                                                                                                                                                                                                                                                                                                                                                                                        |

| Resource<br>manager      | Also referred to as Resman. This software is made available by the manufacturer of the Slot-0 controller and is used to set logical addresses and configure Operational Register addresses in a system.                                                                                                                                                                                                               |

## Conventions

Hexadecimal numbers are represented by the prefix Ox. For example,  $255_{10} = 0$ xFF.

The following icons are used in this manual:

**NOTE:** Information notes are used to call attention to important features or instructions.

**CAUTION:** Caution notices contain directions that must be followed to avoid immediate system damage or loss of data.

## **Chapter I: Introduction**

## **General Description**

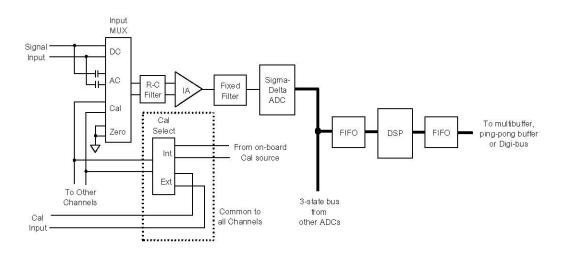

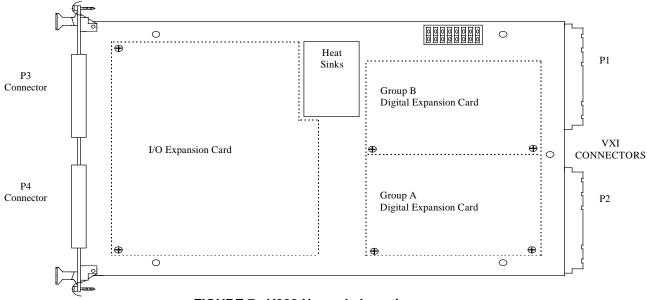

The V200 module provides 16 channels of gain and analog to digital conversion in its base configuration. An architecture for the main card is shown in the accompanying block diagram. The discussion will be keyed to this diagram.

FIGURE 1 - V200 Main Card

The input channels are divided into two groups (A and B), each containing eight or sixteen channels. Data is acquired independently by each group.

Each of the groups consists of 8 or 16 input channels with a Sigma-Delta analog-to-digital converter (ADC), an input multiplexer, an instrumentation amplifier with programmable gain, a gain/attenuator stage (the ADC has an input span of +/-1 volt). **Two**-pole passive filtering is provided for each channel. The outputs of the ADCs are fed into the ADC FIFO. Up to sixteen channels may be synchronously loaded into this FIFO when the "Convert Complete" flag indicates that data is available.

The DSP is signaled by the FIFO control logic when the correct number of channels has been read into the FIFO. The DSP then reads up to sixteen data words, performs limit checking and writes the data to the output FIFO (also called Ping Pong FIFO).

When the appropriate number of datawords have been written to the output FIFO, its contents are transferred to Ping-Pong Buffer Memory, Multibuffer Memory, or the Digi-bus interfaces.

## **Channel Inputs**

The input multiplexer allows one of four inputs to be routed into the channel. These are:

- 1. DC coupled signal input

- 2. AC coupled signal input

- 3. Calibration bus input

- 4. Zero (ground) reference.

An instrumentation amplifier with programmable gain follows the input MUX. This provides common mode rejection and gain. A combination of filtering, attenuation and gain stages follow the instrumentation amplifier, providing overall input spans from +/- 10 volts to +/- 10 millivolts in a 1, 2, 5, 10 sequence.

The Sigma Delta ADC used is an Analog Devices AD7722, running at a conversion rate of up to 200kSamples per second. The AD7722 provides extremely accurate 16-bit conversion. The ADCs for each group are run at the same clock rate. All ADCs within a group are synchronized with each other. Additionally both groups may be run from the same sample clock and both groups may be synchronized.

Synchronization pulses may be applied by the DSPs, via the front panel Sync. Input or via one of the VXI Trigger Lines.

## Clock Generator

The clock for the Sigma-Delta converters runs at 64 times the "sample rate", the input being sampled twice per clock period. This provides an oversampling rate of 128. Thus to achieve a conversion rate of 200kSps a clock rate of 12.8MHz is needed. A Phase Lock Loop, which multiplies a preselected sample clock rate by 64, is provided for Group A. This clock source can be coupled to also run the Group B ADCs.

The input to the Phase Lock Loop (PLL) can be from the External Clock Input on the front panel, from the internal clock source or from the VXI Trigger lines. The internal clock source for the PLL selects a sampling rate in the range of 5 kHz to 200 kHz, in 100 nanosecond increments.

The A/D converter clock source can also be selected by using an on-board crystal controlled oscillator. For this mode, the PLL is bypassed and the crystal frequency is divided to provide the actual sampling rate. The A/D converter can accept clock frequencies in the range of 320KHz to 12.8MHz. This corresponds to sample clock frequencies of 5KHz to 200KHz.

Additionally, groups A and B can be locked together, in which case Group B becomes a slave of Group A.

#### DSP

Each group has a TMS320C50 running at 80MHz. Each DSP has 32k words of Flash RAM in program space and 64k words of static RAM in data space. The DSP program is downloaded into the flash RAM via the VXI bus. This is not user programmable.

The external static RAM is used for storing calibration data, etc.

## Limit Checking

Limit checking is performed by the DSP, and is of the level/slope type or minimum/maximum type. An ADC value (level) and slope (positive or negative) or minimum and maximum is selected by the user before acquisition starts and may not be changed during acquisition. A limit violation can be programmed to cause a transient capture countdown to begin. It can also be routed to the VXI trigger lines or the front panel Trigger Out SMB connector.

## Time Tagging

The contents of an on-board tick counter can be inserted into the data stream (to be written into Multibuffer Memory). This tick count can also be read through the ping pong interface. This tick count allows post-processing verification that no data samples were lost.

## **Ping Pong Memory**

This is a dual-buffered memory, which allows synchronous reads to be made via the VXI bus. While one side of the memory is being filled by the Ping Pong FIFO the other half can be read out across the VXI bus.

After one set of data samples has been written to ping pong a clock pulse is generated which causes the ping pong memory to "flip" and present the last set of samples to the VXI bus. New data for each active channel is then written into the "inboard" side of the memory and so on. This "flip" clock corresponds to a delayed version of the sample clock and may be routed to the VXI trigger lines and used to synchronize data reads by the Slot 0 controller.

The set of registers accessible from the VXI bus are loaded synchronously with the start of a scan and are valid until the start of the next scan. This technique provides the full interval between scans for data access.

## VXI Trigger Lines

Eight of the pins on the P2 connector of the VXI bus are defined as TTL trigger lines. These open collector lines provide a wired-OR function that is suited to their use in communicating event information between modules.

A practical concept in using these lines is that of event sources and event sinks. Events on a specific trigger line may be generated by any one of several modules. One or more modules may be programmed to respond to events, including the source module of the event.

Examples of event sources are sample rate, limit checking, and front-panel external trigger inputs. Examples of event sinks are transient capture triggers to initiate the capture and local storage of a data segment, and sample clocks to synchronize sampling of input signals or outputting of DAC or digital data.

Consider the case where several V200s are required to trigger simultaneously. The occurrence of a limit condition on any of the modules can cause a VXI trigger line to be asserted and a transient capture initiated across all modules. Meanwhile, another trigger line has been programmed as the source for the scan rate.

Trigger lines can be used to synchronize sampling across multiple modules.

#### Multibuffer Memory Option

Each group may have a Multibuffer Memory card. Each card provides 4 or 16 Mbytes of dynamic RAM.

The Multibuffer Memory option provides critical buffering between the Slot-0 processor and the ADC to prevent data loss due to processor latency when switching buffers and processing data. The Multibuffer Memory also can be configured to provide a transient capture function where a fixed block of data is captured in memory based on the occurrence of a trigger event. Possible trigger events might include an external trigger or one or more of some selected analog inputs exceeding a programmed threshold. The number of pre- and post-trigger samples may be selected by the user.

## System Calibration/Diagnostics

In any system, particularly with larger data acquisition systems, verifying the proper functioning of the system and the calibration of analog I/O is essential. Generally, it is possible to check out some digital system components through exercising the hardware under software control.

To audit analog channels to any degree requires that a series of known analog signals be injected into each channel of the system. This can be accomplished either by operator intervention or by providing the capability to switch known calibration signals into the input under software control. Switching of calibration signals by hand can be very time-consuming and is subject to errors.

For these reasons, KineticSystems has chosen an implementation with full end-to-end calibration features. To accomplish this goal with the architecture described, a known signal must be injected at the input to the signal conditioning. This is accomplished by a programmable active attenuator or an external user-supplied front-panel calibration signal.

The fixed-point DSP is used to provide calibration and self-test of each group on the V200.

AC calibration may be accomplished by injecting a precise sine wave into the external cal. Input and capturing a segment of the waveform for analysis.

## **System Configuration Validation**

One of the issues, particularly in larger systems, is ensuring that the proper modules with the proper options are installed and configured in the system. This is especially important when you cannot accurately validate the current system configuration because of system size or physical access to areas in a distributed system. Verifying proper installation can be particularly frustrating when modules of the same type or model number can be configured with a number of internal options. Unfortunately, this is an increasingly common practice because of the high densities that can be achieved today and the relatively large card size of VXI. A related issue is the capability to identify and trace the history of specific modules within a larger system.

The VXI standard requires (or in some cases, suggests) that certain register conventions be followed. These register conventions partially address these issues. Standardized registers include the manufacturer ID assigned by the VXI Consortium, a device-type or model identifier, a serial number, and a version number or revision number for hardware and firmware.

An extension of this concept provides a module option identifier as well as some amount of userwriteable EEPROM (Electrically Erasable Programmable Read Only Memory). The EEPROM provides the capability to record in nonvolatile memory any option, calibration, or other module-specific information that may be important to system operation and/or maintenance.

Since these registers are accessible by software, it is possible to develop software to verify system configuration at startup, as well as track modules for maintenance purposes.

## Self-Test

Upon reset or on command the V200 can perform a self-test function. When a self-test is initiated the DSP for each group switches through all possible gain settings for each of the channels. For each gain, precision voltages corresponding to plus and minus full scale and zero volts are applied to the channels. The resulting ADC value for each input voltage is compared to test limits. If any test fails, SYSFAIL remains asserted. The DSPs may be interrogated for details of the self-test results.

## **Channel Calibration**

The DSP performs channel calibration on command. This consists of injecting the appropriate plus and minus full-scale voltages into the channel as well as zero volts. The DSP averages several readings and calculates the transfer function of the channel. The results of the calculation can be read back from the DSP.

Channels must be configured before initiating calibration.

# **Chapter II: Unpacking and Installation**

At KineticSystems, static precautions are observed from production, test, and packaging of the module. This includes using static proof mats and wrist straps. Please observe these same precautions when unpacking and installing the module whenever possible.

**CAUTION:** To guard against electrostatic discharge if no wrist straps are available, touch the anti-static bag to a metal part of the VXI chassis before removing the V200.

The Model V200 is shipped in an anti-static bag within a Styrofoam packing container. Carefully remove the module from its static-proof bag and prepare to set the logical address switches to the appropriate value.

## Configuration

There is one set of user configurable switches on the V200, shown in figure 2. All eight switches, #1 (MSB) to #8 (LSB), are for the logical address. The logical address may be set from 1 to 254 as a statistically configured device. If the V200 is a statistically configured device, it is the user's responsibility to ensure that no two modules are set to the same logical address. Please refer to figure 3 for setting switches. If the module is set for logical address 255 (all switches open), then the V200 will be dynamically configured by the resource manager. A logical address of 0 is not valid since it is reserved for the Slot-0 controller. Logical address 255 is the factory default setting. Please refer to Appendix D for a composite drawing showing strap and switch locations on the V200.

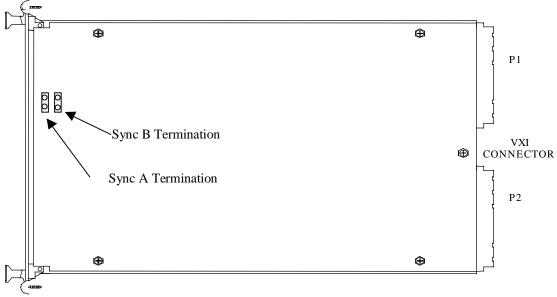

## Front Panel Sync Signal Termination

The V200 can accept a Sync pule from an external source. Two SMB connections are available on the front panel to synchronize Group A and Group B ADCs. These inputs are terminated to +5 volts through a 1000 ohm resistor. If multiple V200s are tied together using the Sync signals, some of the termination resistors must be removed. Only the V200 that sources the Sync signal should have the termination resistor connected, all others should have them removed.

Two straps are provided on the V200 for enabling and disabling the connection of the 1000ohm resistor. One resistor is for the Group A Sync signal and the other is for Group B. If the straps are installed, the termination resistors are connected to the Sync signal. Removal of the strap disconnects the Sync signal from the termination resistor. The following diagram, figure 4, shows the location of the two straps. Please refer to Appendix D for a composite drawing showing strap and switch locations on the V200.

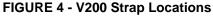

#### +24 Volt Front Panel Connection

The V200 contains a strap option that allows a +24 volt supply signal to be connected to the P4 connector on the front panel. This signal is on contact 23 and is used to enable the 24-volt supply to power an ICP termination panel. This strap is factory configured to disable the 24-volt supply. If an ICP termination panel is used with the V200, this strap must be placed in the enable position. The following diagram shows the location of the +24 volt strap on the V200. Please refer to Appendix D for a composite drawing showing strap and switch locations on the V200.

FIGURE 5 - V200 +24 Volt Strap Location

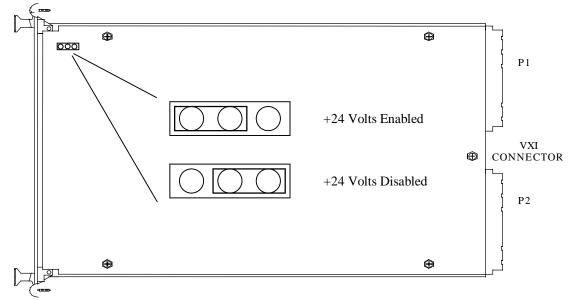

#### Motorola/Intel Data Format

The V200 is capable of transferring data in either the Motorola or Intel data format. For writing/reading longwords (32-bit values) to/from the V200, the format does not change. The change in format occurs when accessing shortwords (16-bit values) from 32-bit register locations. The following diagram shows a 32-bit longword.

| High Sh       | High Shortword |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|---------------|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Offset        | 31             | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| R/W           | D31            | D30 | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| Low Shortword |                |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Offset        | 15             | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |

| R/W           | D15            | D14 | D13 | D12 | D11 | D10 | D09 | D08 | D07 | D06 | D05 | D04 | D03 | D02 | D01 | D00 |

An access to the long word address at offset 0 accesses bits 31 through 0 with one VXI transfer. Accesses to this register vary depending on the Data Format selected and the offset at which the register is accessed.

When the Motorola Data Format is selected, a shortword access to offset 0 of this register returns the high shortword, data bits D31 through D16. A shortword access to offset 2 of this register returns the low shortword, data bits D15 through D00.

When the Intel Data Format is selected, a shortword access to offset 0 of this register returns the low shortword, data bits D15 through D00. A shortword access to offset 2 of this register returns the high shortword, data bits D31 through D16.

The following diagram shows the location of the Motorola/Intel Data Format strap on the V200. Please refer to Appendix D for a composite drawing showing strap and switch locations on the V200.

FIGURE 6 - V200 Motorola/Intel Data Format Strap Location

#### I/O Expansion Cards

The V200 has I/O expansion cards available to increase the number of channels or add additional functionality to the card. These options may be purchased as factory or field upgrades. In the case of factory upgrades, the I/O expansion card is tested and integrated with a base card of the V200. Usually, the base card of the V200 is ordered with the factory upgrade. However, the base card may also be returned to the factory for integration. In the case where the base card has already been purchased, this factory upgrade option is recommended. However, a field upgrade kit may also be purchased.

Refer to Figure 7 while installing the field upgrade of the I/O expansion card.

Place the I/O expansion card into the two inter-board connectors located on the main card. The inter-board connectors are shrouded and keyed to help prevent a misalignment of pins. Two screws are provided with the field upgrade kit to securely fit the card into place. Place the shield back over the card.

FIGURE 7 - V200 Upgrade Locations

## Digital Expansion Cards

The V200 is capable of accepting digital expansion cards to add functionality to the card. These options may be purchased as a factory upgrade or as a field upgrade. The current upgrades consist of a 4 megabyte multibuffer and a 16-megabyte multibuffer. A multibuffer card is required for each group of ADC channels. If only the Group A channels need the multibuffer capability, only one multibuffer card is required.

## **Module Insertion**

The V200 is a C-sized, single width, VXI*bus* module. Except for Slot-0, it can be mounted in any unoccupied slot in a C-size VXI*bus* mainframe.

**CAUTION:** TURN MAINFRAME POWER OFF WHEN INSERTING OR REMOVING MODULE.

If the mainframe does not have an autoconfiguring backplane, special care is necessary when installing the V200. To insure proper interrupt acknowledge cycles from the V200 module, the daisy-chain Interrupt Acknowledge jumper must be removed before the module is installed in a slot. Conversely, daisy-chain jumpers must be installed in any empty slot between the V200 and the Slot-0 Controller.

**NOTE:** Remember to remove Interrupt Acknowledge daisy-chain jumpers prior to inserting this module in the backplane or use an autoconfiguring backplane.

Once the V200 is placed in the appropriate slot, make sure the screws located on the front panel are screwed into the mainframe. The shield of the high-density connectors are connected to the front panel and ground to provide additional protection from static electricity. To provide maximum protection, the front panel should be screwed into the chassis. Otherwise, the static electricity must discharge through the V200 potentially causing unexpected behavior.

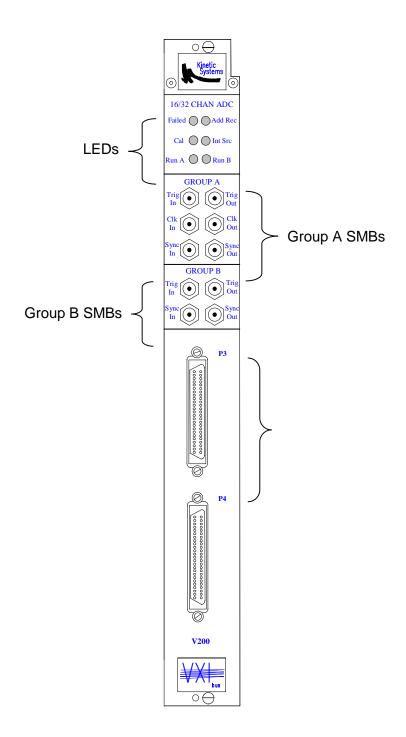

## Front Panel Description

Please refer to Figure 8 for the following section.

#### **LED**s

After power up, the Failed LED will be on for at most five seconds while self-tests are being run. During this time, the ADC, DSP, and RUN LEDs may also turn on periodically. If the Failed LED stays on after five seconds, then the self-test failed. When self-tests are complete, all other LEDs will be off.

| LED      | Description                                                                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Failed   | The LED will turn on whenever self-tests are run.                                                                                                                |

| Add Rec. | Add Rec. (Address Received) LED lights to indicate the V200 is being accessed through VXI in either A16 or A32 address space.                                    |

| Cal      | The Cal LED will light while the V200 is executing a calibration sequence.<br>This LED is illuminated for both the Group A and Group B calibration<br>sequences. |

| Int. Src | The Int. Src LED will light while the V200 is requesting an interrupt.                                                                                           |

| Run A    | The Run A LED is lit as long as the Group A ADCs are in the RUN mode transferring data to either the ping-pong memory or the multibuffer memory.                 |

| Run B    | The Run B LED is lit as long as the Group B ADCs are in the RUN mode transferring data to either the ping-pong memory or the multibuffer memory.                 |

#### Connectors

The V200 has two 50 pin, high-density connectors located on the front panel. The P4 connector has 16 differential inputs as well as a reference input. This connector, which contains connector pins, provides access to channels 1 through 16 of the V200. The connector labeled P3 on the V200 may be either a pin or socket connector. For a V200 with only 16 ADC channels, this connector is a socket connector and provides access to the buffered ADC signals after amplification/attenuation. For a V200 with 32 ADC channels, this connector is a pin connector and provides access to the 16 differential inputs for the additional 16 ADC channels. See Figure 8 on page 14, Figure 9 on page 97, and Tables 2-4 on pages 98-100 for the precise pinout descriptions.

A total of 10 SMB connectors are provided on the front panel of the V200. Six of the SMBs are located in a block for Group A and four are in a block for Group B. The following describes the function of each SMB located in the corresponding ADC group.

FIGURE 8 - V200 Front Panel

## Group A SMBs

There are six SMBs for Group A. The Group A Trigger In and Group A Trigger Out SMBs are tied together and received by a 74F14 buffer. These inputs are tied to +5 volts through a 10K $\Omega$  resistor. This is a TTL level input with a minimum pulse width of 200 nanoseconds. The assertion of this signal is true when the input is low. This signal can be programmed to assert a VXI TTL trigger line. The assertion of this trigger line can then be used to start a run mode or trigger a transient capture. Please refer to the Group A Trigger Reception Register description on page 39 for additional information. The Trigger Out SMB can then be used to daisy chain the trigger signal to other V200s.

The **Group A Clock In** signal is received by a pair of 74F14 buffers. This clock input can be used to supply either the Sample Clock for the Group A/B ADCs or the high frequency oversampling clock to the ADCs. Although these signals are located in the Group A block, they can actually supply the clock for both Group A and Group B. For this mode, the Group A and Group B ADCs must be locked into one large group. The input is tied to +5 volts through a 10K resistor. This is a TTL level input that can be used to provide an external sample clock or the oversampling clock to the ADCs. The clock input frequency can range from 10KHz to 200 kHz when supplying the sample clock and should maintain a 40% to 60% duty cycle. If the clock input is to supply the high frequency oversampling clock, this input can range from 640 kHz to 12.8 MHz and should maintain a 40% to 60% duty cycle. When this input is used as a sample clock, a Phase Locked Loop (PLL) is used to multiply the input frequency by 64 to obtain the oversampling clock for the ADCs.

The **Group A Clock Out** SMB is internally connected to the ADC oversampling clock for Group A. This is a TTL level output and is driven by a 74F153 gate. When an external over sample clock is used, a selectively divided 12.8 MHz clock is switched out to this SMB.

The **Group A Sync** signal is received with a 74F04 buffer. This signal is configured at the factory with a  $1K\Omega$  pull-up resistor to +5 volts. Optionally, this signal may be unterminated by removing the strap to the pull-up resistor. When a V200 is the source of the Sync signal, the V200 drives the Sync signal with a 74F06 open-collector device. When used as an input to the V200, this signal is asserted when low and must have a minimum pulse width of 200 nanoseconds. When this pulse is received, all of the Group A ADCs are synchronized. After the sync pulse is applied, whether internally or externally generated, the ADCs within that group are synchronized to provide simultaneous sampling. The Group A Sync Out signal is internally connected to the synchronization signal on the Group A ADCs. This is a TTL level signal driven by a 74F04 gate.

The **Group A Trigger In** and **Trigger Out** SMBs are tied together on the V200 and provide a mechanism for triggering various V200 operations. These operations include starting ADC run mode and triggering a transient capture. In these instances, the V200 receives these signals to provide the indicated function. Also, these SMBs can be configured as outputs from the V200 and can be asserted when a Ping-Pong Flip occurs or an ADC limit violation occurs. Please refer to the Group A Trigger Reception Register and Group A Trigger Source Register descriptions for additional information regarding the capabilities of asserting/receiving the Front Panel trigger signals.

## Group B SMBs

There are four SMBs for Group B. The Group B Trigger In and Group B Trigger Out SMBs are tied together and received by a 74F14 buffer. These inputs are tied to +5 volts through a 10K $\Omega$  resistor. This is a TTL level input with a minimum pulse width of 200 nanoseconds. The assertion of this signal is true when the input is low. This signal can be programmed to assert a VXI TTL trigger line. The assertion of this trigger line can then be used to start a run mode or trigger a transient capture. Please refer to the Group B Trigger Reception Register description for additional information. The Trigger Out SMB can then be used to daisy-chain the trigger signal to other V200s.

The **Group B Sync** signal is received with a 74F04 buffer. This signal is configured at the factory with a  $1K\Omega$  pull-up resistor to +5 volts. Optionally, this signal may be unterminated by removing the strap to the pull-up resistor. When a V200 is the source of the Sync signal, the V200 drives the Sync signal with a 74F06 open-collector device. When used as an input to the V200, this signal is asserted when low and must have a minimum pulse width of 200 nanoseconds. When this pulse is received, all of the Group B ADCs are synchronized. After the sync pulse is applied, whether internally or externally generated, the ADCs within that group are synchronized to provide simultaneous sampling. The Group B Sync Out signal is internally connected to the synchronization signal on the Group B ADCs. This is a TTL level signal driven by a 74F04 gate.

The **Group B Trigger In** and **Trigger Out** SMBs are tied together on the V200 and provide a mechanism for triggering various V200 operations. These operations include starting ADC run mode and triggering a transient capture. In these instances, the V200 receives these signals to provide the indicated function. Also, these SMBs can be configured as outputs from the V200 and can be asserted when a Ping-Pong Flip occurs or an ADC limit violation occurs. Please refer to the Group B Trigger Reception Register and Group B Trigger Source Register descriptions for additional information regarding the capabilities of asserting/receiving the Front Panel trigger signals.

# **Chapter III: Programming Information**

## VXIbus Addressing

The V200 is classified as an extended register-based device, which means it has registers that occupy A16 and A32 space. In accordance with the VXI specification, A16 space means that only 16 address bits are decoded by the V200. A32 space means that 32 address bits are decoded by the V200.

The configuration registers are located in A16 space and include the standard registers defined by VXI as well as additional general-purpose registers. From these registers information about the specific module can be read, the base address for the A32 registers can be controlled, and the interrupt level can be set. For example, by reading certain registers in A16 space, the following information about this module can be found just by knowing the module's logical address:

| Manufacturer:            | KineticSystems |

|--------------------------|----------------|

| Module Type:             | V200           |

| <b>Base Card Option:</b> | AA11           |

| Serial Number:           | 20             |

| Firmware Version:        | 1.0            |

| Hardware Version:        | 1.0            |

In general, any configuration register can be accessed simply by knowing the module's logical address (set by the logical address switches) and the register's offset by using the following equation. A complete list of A16 register descriptions and their offsets is available on page 19. The following equation is used to determine the actual A16 address:

A16\_Address = 0xC000 + (Logical\_Address · 0x40) + A16\_Register\_Offset

As defined by the VXI specification, these Configuration Registers will support D16 transfers only.

**Manufacturer**: can be found by looking at bits 11 through 0 at register offset 0x0. If the value is 0xF29, this indicates that the module was built by KineticSystems.

**Module Type:** can be found by looking at bits 11 through 0 at register offset 0x2. If the value is a binary coded decimal (BCD) number 200, this indicates that the module is a V200.

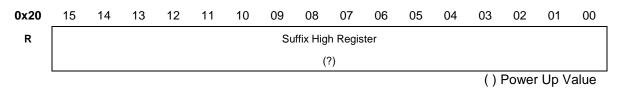

**Base Card Option:** can be found by reading the four-character string in registers located at offsets 0x20 and 0x22. If the string "AA" is found at offset 0x20 and "11" is found at offset 22, then the specific type of module is the V200-AA11 meaning this module is a V200 with 16 channels. The suffix registers are additional registers defined by KineticSystems to aid in identifying a module.

**Serial Number:** can be found reading the 32-bit, unsigned number stored in registers at offsets 0xA and 0xC. For example, if a the serial number was 20, the values in the Serial Number High Register would be 0x0 and the value in the Serial Number Low Register would be 0x14.

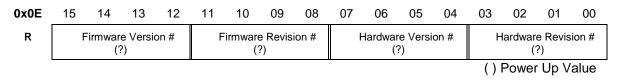

**Firmware Version:** can be found by reading the binary coded decimal (BCD) number stored in bits 15 through 8 of the Version Number Register at offset 0xE.

**Hardware Version:** can be found by reading the BCD number stored in bits 7 through 0 of the Version Number Register at offset 0xE.

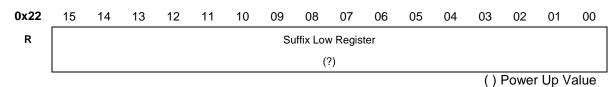

In addition to the Suffix Registers, KineticSystems has left registers at offsets 0x24 through 0x3E open for user definition. These User Defined Registers can also be used to identify the module (i.e., with an internal identification number). These registers can only be written one at a time and only at 3ms intervals. However, once they have been written, the data is retained even after power has been removed.

The Operational Registers are located in A32 space and include the registers specific to V200 modules. This address space is configured by the resource manager. In general, any Operational Register can be accessed simply by knowing the value in the modules Offset Register (Configuration register in A16 space at offset 0x6) and using the following equation. A complete list of A32 register descriptions and their offsets is available starting on page 29.

A32\_Address = (Offset\_Register\_Value · 0x10000) + A32\_Register\_Offset

All Operation Registers support D16, D32, D16 BLK and D32 BLK transfers.

The V200 can be configured to respond with either Intel addressing or Motorola addressing. The factory default is Motorola addressing. For Motorola addressing, a shortword address to a longword location is as follows:

## V200 Configuration Registers, A16 Space

#### ID/Logical Address Register

| 0x00 | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02    | 01   | 00   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|------|------|

| R    | (0) | (1) | (0) | (1) | (1) | (1) | (1) | (1) | (0) | (0) | (1) | (0) | (1) | (0)   | (0)  | (1)  |

|      |     |     |     |     |     |     |     |     |     |     |     |     | ()  | Power | Up V | alue |

On READ transactions the V200 returns 0x5F29.

| Bit(s) | Mn  | Mnemonic          |    |    |    |                                                        | Meaning |        |      |       |       |     |     |     |     |     |  |

|--------|-----|-------------------|----|----|----|--------------------------------------------------------|---------|--------|------|-------|-------|-----|-----|-----|-----|-----|--|

| 15,14  | Dev | Device Class      |    |    |    | This is an Extended Register-Based Device.             |         |        |      |       |       |     |     |     |     |     |  |

| 13,12  | Ado | Address Space     |    |    |    | This module requires the use of A16/A32 address space. |         |        |      |       |       |     |     |     |     |     |  |

| 11-00  | Ma  | Manufacturer's ID |    |    |    |                                                        | 0xF29   | 9) for | Kine | ticSy | stems | 5.  |     |     |     |     |  |

| 0x00   | 15  | 14                | 13 | 12 | 11 | 10                                                     | 09      | 08     | 07   | 06    | 05    | 04  | 03  | 02  | 01  | 00  |  |

| w      |     |                   |    |    |    |                                                        |         |        | LA7  | LA6   | LA5   | LA4 | LA3 | LA2 | LA1 | LA0 |  |

() Power Up Value

For WRITE transactions, bits fifteen through eight are not used. These bits may be written with any data pattern. In Dynamically Configured systems (and the Logical Address switches were set to a value of 255), bits seven through zero are written with the Logical Address value. This register is used by the resource manager to dynamically set a module's logical address.

## Device Type Register

| 0x02 | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |

|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| R    | (0) | (1) | (0) | (1) | (0) | (0) | (1) | (0) | (0) | (0) | (0) | (0) | (0) | (0) | (0) | (0) |

() Power Up Value

This READ ONLY register returns 0x5200.

| Bit(s) | Mnemonic        | Meaning                                                 |

|--------|-----------------|---------------------------------------------------------|

| 15-12  | Required Memory | The V200 requires 64 Mbytes of additional memory space. |

| 11-00  | Model Code      | Identifies this device as a V200 (0x200).               |

## Status/Control Register

| <sup>04</sup> 16 | 15         | 14    | 13  | 12  | 11  | 10  | 09  | 80  | 07  | 06  | 05  | 04  | 03    | 02    | 01          | 00            |

|------------------|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|-------|-------------|---------------|

| Mixed            | A32<br>ENA | Modid |     |     |     |     |     |     |     |     |     |     | Ready | Pass  | Sys<br>Inb. | Soft<br>Reset |

|                  | (0)        | (0)   | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (0)   | (0)   | (0)         | (0)           |

|                  |            |       |     |     |     |     |     |     |     |     |     |     | ()    | Power | · Up V      | alue          |

The bit assignments for the Status/Control register are defined as follows:

| Bit(s) | Mnemonic   | Meaning                                                                                                                                                                                                                                                                                       |

|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | A32 ENA    | This bit is written with a "1" to enable A32 addressing and reset to "0" to disable these registers. Reads of this bit indicate its current state. This bit is reset to "0" by the assertion of SYSRESET*. This bit is set by the resource manager once the offset register has been written. |

| 14     | Modid*     | This read only bit is set to a "1" if the module is not selected with the MODID line on P2. A "0" in this bit location indicates the device is selected via a high state on its P2 MODID line. This bit is used by the resource manager to dynamically configure the V200.                    |

| 13-04  | Not Used   | These bits are not used and are read as "1s".                                                                                                                                                                                                                                                 |

| 03     | Ready      | A "1" in this bit indicates the successful completion of register initialization.                                                                                                                                                                                                             |

| 02     | Pass       | A "0" indicates the V200 has failed or is currently executing its self-test. A "1" in this bit indicates the module's self-test has passed.                                                                                                                                                   |

| 01     | Sys. Inb.  | (Sysfail Inhibit) Writing a "1" to this bit disables the V200 from driving the SYSFAIL* line. Reads of this bit indicate its current state.                                                                                                                                                   |

| 00     | Soft Reset | Writing a "1" to this bit forces the device into the Soft Reset State.<br>While in this state, the module will only allow access to its<br>Configuration Registers. Writing a "0" to this bit will the signal the<br>V200 to begin executing its self-test                                    |

**NOTE:** The Soft Reset bit must be cleared along with the Pass and Ready bits set before any access to the Operational Registers is allowed.

**NOTE:** The A32 ENA bit must be set to allow access to the module's Operational Registers.

#### **Offset Register**

|      | A31              | A30              | A29              | A28              | A27              | A26              |     |     |     |     |     |     |     |       |      |      |

|------|------------------|------------------|------------------|------------------|------------------|------------------|-----|-----|-----|-----|-----|-----|-----|-------|------|------|

| 0x06 | 15               | 14               | 13               | 12               | 11               | 10               | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02    | 01   | 00   |

| R/W  | OFF<br>15<br>(0) | OFF<br>14<br>(0) | OFF<br>13<br>(0) | OFF<br>12<br>(0) | OFF<br>11<br>(0) | OFF<br>10<br>(0) | (0) | (0) | (0) | (0) | (0) | (0) | (0) | (0)   | (0)  | (0)  |

|      |                  |                  |                  |                  |                  |                  |     |     |     |     |     |     | ()  | Power | Up V | alue |

After SYSRESET\* and prior to self-test all bits are reset to "0". Otherwise, a read or write defines the base address of the module's A32 registers. Bits 09-00 of this register are not used and should always be written with zeros. As shown above bits 15-10 map directly onto VXI address lines A31-A26. For example, if bits OFF15-0FF10 contain 010000 binary, the base address for the module's Operational Registers becomes 0x40000000.

#### Attribute Register

| 0x08 | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02         | 01         | 00         |

|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------|------------|------------|

| R    | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | IR*<br>(0) | IH*<br>(1) | IC*<br>(0) |

|      |     |     |     |     |     |     |     |     |     |     |     |     | ()  | Power      | · Up V     | alue       |

This read only register returns 0xFFFA on READ transactions. Write transactions to this register have no effect and its usage is reserved for future definition.

| Bit(s) | Mnemonic | Meaning                                                                                       |

|--------|----------|-----------------------------------------------------------------------------------------------|

| 15-03  | Reserved | These bits are read as "1s" and reserved for future definition.                               |

| 02     | IR*      | This bit is read as a "0" to signify that the V200 is capable of generating interrupts.       |

| 01     | IH*      | This bit is read as a "1" and indicates the V200 is not capable of Interrupt Handler Control. |

| 00     | IS*      | This bit is set to "0" to indicate the V200 has Interrupt Status Reporting capability.        |

#### Serial Number High

| 0x0A  | 15               | 14               | 13               | 12               | 11               | 10               | 09               | 08               | 07               | 06               | 05               | 04               | 03               | 02               | 01               | 00               |

|-------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| R     | SER<br>31<br>(?) | SER<br>30<br>(?) | SER<br>29<br>(?) | SER<br>28<br>(?) | SER<br>27<br>(?) | SER<br>26<br>(?) | SER<br>25<br>(?) | SER<br>24<br>(?) | SER<br>23<br>(?) | SER<br>22<br>(?) | SER<br>21<br>(?) | SER<br>20<br>(?) | SER<br>19<br>(?) | SER<br>18<br>(?) | SER<br>17<br>(?) | SER<br>16<br>(?) |

| Seria | l Nu             | mbe              | er Lo            | w                |                  |                  |                  |                  |                  |                  |                  |                  | ()               | Power            | Up V             | alue             |

| 0x0C  | 15               | 14               | 13               | 12               | 11               | 10               | 09               | 08               | 07               | 06               | 05               | 04               | 03               | 02               | 01               | 00               |

| R     | SER<br>15<br>(?) | SER<br>14<br>(?) | SER<br>13<br>(?) | SER<br>12<br>(?) | SER<br>11<br>(?) | SER<br>10<br>(?) | SER<br>9<br>(?)  | SER<br>8<br>(?)  | SER<br>7<br>(?)  | SER<br>6<br>(?)  | SER<br>5<br>(?)  | SER<br>4<br>(?)  | SER<br>3<br>(?)  | SER<br>2<br>(?)  | SER<br>1<br>(?)  | SER<br>0<br>(?)  |

|       |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  | ()               | Power            | Up V             | alue             |

These READ ONLY registers indicate the serial number of the module. Each module is given a unique serial number. The serial number is represented by a 32-bit unsigned integer. The least significant bits (LSBs) reside in the Serial Number Low register while the most significant bits (MSBs) are in the Serial Number High register. Writing to these registers will have no effect and its use is reserved. For example, assume the module's serial number is 0x10064 (65636). A read of the Serial Number High register returns 0x0001 (1  $\Rightarrow$  1 \* 65536); and the Serial Number Low register returns 0x0064 (100).

#### Version Number Register

This READ ONLY register indicates the hardware and firmware revision number of the module. A write to this register has no effect on its contents. The fields of this register are explained as follows:

| Bits  | Mnemonic            | Meaning                  |

|-------|---------------------|--------------------------|

| 15-12 | Firmware Version #  | Firmware Version Number  |

| 11-08 | Firmware Revision # | Firmware Revision Number |

| 07-04 | Hardware Version #  | Hardware Version Number  |

| 03-00 | Hardware Revision # | Hardware Revision Number |

The combination of Firmware Version Number and Firmware Revision Number indicate the module's firmware version level. These two fields contain two four-bit integers and are joined to form the level.

## Interrupt Status Register

| 0x1A | 15                         | 14                        | 13                       | 12  | 11                         | 10 | 09                       | 08                        | 07 | 06 | 05 | 04                    | 03                    | 02 | 01 | 00 |

|------|----------------------------|---------------------------|--------------------------|-----|----------------------------|----|--------------------------|---------------------------|----|----|----|-----------------------|-----------------------|----|----|----|

| R    | GPB<br>XSNT<br>CMPL<br>(0) | GPB<br>BUF<br>FULL<br>(0) | GPB<br>LMT<br>ALM<br>(0) | BUF | GPA<br>XSNT<br>CMPL<br>(0) | -  | GPA<br>LMT<br>ALM<br>(0) | GPA<br>BUF<br>FLIP<br>(0) |    |    | I  | Logical<br><b>(0x</b> | Addres:<br><b>FF)</b> | 5  |    |    |

This READ ONLY register is defined as follows:

| Bit(s) | Mnemonic      | Meaning                                                                                                                                                                                                                                                                        |

|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | GPB XSNT      | Group B Transient Complete is a read-only bit set when a transient CMPL capture operation is completed by the post-trigger counter decrementing to zero after a transient event. This bit is cleared by an I/O read of this register or by an interrupt acknowledge cycle.     |

| 14     | GPB BUF FULL  | Group B Buffer Full is a read-only bit set when a multibuffer<br>operation causes the setting of one of the segment full flags in<br>the Group B Multibuffer Control Register. This bit is cleared<br>by an I/O read of this register or by an interrupt acknowledge<br>cycle. |

| 13     | GPB LMT ALM   | Group B Limit Alarm is a read-only bit set when a limit<br>violation is detected by the Group B DSP. This limit is<br>programmed prior to enabling the ADCs. This bit is cleared<br>by an I/O read of this register or by an interrupt acknowledge<br>cycle.                   |

| 12     | GPB BUF FLIP  | Group B Buffer Flip is a read-only bit set whenever a complete ADC scan has completed and the ping-pong buffer is flipped. This bit is cleared by an I/O read to this register or by an interrupt acknowledge cycle.                                                           |

| 11     | GPA XSNT CMPL | Group A Transient Complete is a read-only bit set when a transient capture operation is completed by the post-trigger counter decrementing to zero after a transient event. This bit is cleared by an I/O read of this register or by an interrupt acknowledge cycle.          |

| 10     | GPA BUF FULL  | Group A Buffer Full is a read-only bit set when a multibuffer<br>operation causes the setting of one of the segment full flags in<br>the Group A Multibuffer Control Register. This bit is cleared<br>by an I/O read of this register or by an interrupt acknowledge<br>cycle. |

() Power Up Value

#### Model V200

| Bit(s) | Mnemonic        | Meaning                                                                                                                                                                                                                                                      |

|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9      | GPA LMT ALM     | Group A Limit Alarm is a read-only bit set when a limit<br>violation is detected by the Group A DSP. This limit is<br>programmed prior to enabling the ADCs. This bit is cleared<br>by an I/O read of this register or by an interrupt acknowledge<br>cycle. |

| 8      | GPA BUF FLIP    | Group A Buffer Flip is a read-only bit set whenever a complete<br>ADC scan has completed and the ping-pong buffer is flipped.<br>This bit is cleared by an I/O read to this register or by an<br>interrupt acknowledge cycle.                                |

| 07-00  | Logical Address | These bits contain the Logical Address of the V200 during an interrupt acknowledge cycle. These bits are read as all ones during a non-interrupt acknowledge cycle.                                                                                          |

During an interrupt acknowledge cycle the V200 enables this register onto the D15-D00 data lines. As shown above, the data returned will indicate the current interrupt status as well as the V200s current logical address. Please note that since any enabled source can generate an interrupt, more than one status bit can be set during the acknowledge cycle.

Enabling interrupts, disabling the Interrupt Mask, and selecting an Interrupt Request Line are controlled by the Interrupt Control Register

The Interrupt Control Register will mask (prevent) or unmask (allow) the setting of bits 08-15 in the Interrupt Status Register accordingly.

## Interrupt Control Register

| 0x1C | 15                         | 14                         | 13                        | 12                         | 11                         | 10                         | 09                        | 08                         | 07         | 06  | 05          | 04          | 03          | 02  | 01  | 00  |

|------|----------------------------|----------------------------|---------------------------|----------------------------|----------------------------|----------------------------|---------------------------|----------------------------|------------|-----|-------------|-------------|-------------|-----|-----|-----|

| R    | MSK<br>GPB<br>XCMP*<br>(1) | MSK<br>GPB<br>BFUL*<br>(1) | MSK<br>GPB<br>LMT*<br>(1) | MSK<br>GPB<br>BFLP*<br>(1) | MSK<br>GPA<br>XCMP*<br>(1) | MSK<br>GPA<br>BFUL*<br>(1) | MSK<br>GPA<br>LMT*<br>(1) | MSK<br>GPA<br>BFLP*<br>(1) | EN*<br>(1) | (1) | IRQ2<br>(1) | IRQ1<br>(1) | IRL0<br>(1) | (1) | (1) | (1) |

() Power Up Value

Using this register to control interrupts is defined as follows:

| Bit(s) | Mnemonic         | Meaning                                                                                                                                                                                                                                                              |

|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | MSK GPB<br>XCMP* | A "1" in this bit masks (prevents) the Group B Transient Complete<br>Interrupt Status bit from generating an interrupt request. This bit<br>must be written with a "0" to allow the Group B Transient Complete<br>Interrupt Source to generate an interrupt request. |

| 14     | MSK GPB<br>BFUL* | A "1" in this bit masks (prevents) the Group B Buffer Full Interrupt<br>Status bit from generating an interrupt request. This bit must be<br>written with a "0" to allow the Group B Buffer Full to generate an<br>interrupt request                                 |

| 13     | MSK GPB<br>LMT*  | A "1" in this bit masks (prevents) the Group B Limit Alarm bit from generating an interrupt request. This bit must be written with a "0" to allow the Group B Limit Alarm to generate an interrupt request.                                                          |

| 12     | MSK GPB<br>BFLP* | A "1" in this bit masks (prevents) the Group B Buffer Flip bit from generating an interrupt request. This bit must be written with a "0" to allow the Group B Buffer Flip to generate an interrupt request.                                                          |

| 11     | MSK GPA<br>XCMP* | A "1" in this bit masks (prevents) the Group A Transient Complete<br>Interrupt Status bit from generating an interrupt request. This bit<br>must be written with a "0" to allow the Group A Transient Complete<br>Interrupt Source to generate an interrupt request. |

| 10     | MSK GPA<br>BFUL* | A "1" in this bit masks (prevents) the Group A Buffer Full Interrupt<br>Status bit from generating an interrupt request. This bit must be<br>written with a "0" to allow the Group A Buffer Full to generate an<br>interrupt request.                                |

| 9      | MSK GPA<br>LMT*  | A "1" in this bit masks (prevents) the Group A Limit Alarm bit from generating an interrupt request. This bit must be written with a "0" to allow the Group A Limit Alarm to generate an interrupt request.                                                          |

| 8      | MSK GPA<br>BFLP* | A "1" in this bit masks (prevents) the Group A Buffer Flip bit from generating an interrupt request. This bit must be written with a "0" to allow the Group A Buffer Flip to generate an interrupt request.                                                          |

| Bit(s) | Mnemonic        | Meaning                                                                                                                                                                        |                                                                                                                                                            |                |                |                        |  |  |  |  |

|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------------------|--|--|--|--|

| 7      | EN*             | A one in this bit is used to disable interrupt generation. This bit<br>prevents any source from generating an interrupt. A zero in this<br>field enables interrupt generation. |                                                                                                                                                            |                |                |                        |  |  |  |  |

| 6      | Not Used        | V20                                                                                                                                                                            | This bit is reserved for use during interrupt handling. Since the V200 is not capable of interrupt handling, this bit should always be written with a "1". |                |                |                        |  |  |  |  |

| 5-3    | IRL2*-<br>IRL0* | This 3-bit field selects the VXI <i>bus</i> interrupt line associated with the interrupt according to the following table:                                                     |                                                                                                                                                            |                |                |                        |  |  |  |  |

|        |                 |                                                                                                                                                                                | IRL2*<br>(D05)                                                                                                                                             | IRL1*<br>(D04) | IRL0*<br>(D03) | Interrupt Request Line |  |  |  |  |

|        |                 |                                                                                                                                                                                | 0                                                                                                                                                          | 0              | 0              | IRQ7                   |  |  |  |  |

|        |                 |                                                                                                                                                                                | 0                                                                                                                                                          | 0              | 1              | IRQ6                   |  |  |  |  |

|        |                 |                                                                                                                                                                                | 0                                                                                                                                                          | 1              | 0              | IRQ5                   |  |  |  |  |

|        |                 |                                                                                                                                                                                | 0                                                                                                                                                          | 1              | 1              | IRQ4                   |  |  |  |  |

|        |                 |                                                                                                                                                                                | 1                                                                                                                                                          | 0              | 0              | IRQ3                   |  |  |  |  |

|        |                 |                                                                                                                                                                                | 1                                                                                                                                                          | 0              | 1              | IRQ2                   |  |  |  |  |

|        |                 |                                                                                                                                                                                | 1                                                                                                                                                          | 1              | 0              | IRQ1                   |  |  |  |  |

|        |                 |                                                                                                                                                                                | 1                                                                                                                                                          | 1              | 1              | Disconnected           |  |  |  |  |

| 2-0    | Not Used        | These bits are reserved for selecting an interrupt handler line. The V200 does not have interrupt handler capabilities, these bits should always be written with "1s".         |                                                                                                                                                            |                |                |                        |  |  |  |  |

All bits in this register are set to "1" on the assertion of SYSRESET\* or if the SOFT RESET bit in the Status/Control register is written with a "1". If any condition is to generate an interrupt, the appropriate interrupt masks must be set to disable the mask, IREN\* bits must be cleared, and IRL2\*-IRL0\* must be a binary code value other than 111. An interrupt request pending on any particular line is cleared by the assertion of SYSRESET\*, putting the module into Soft Reset, changing IRL2\*-IRL0\*, or if the interrupt is properly acknowledged.

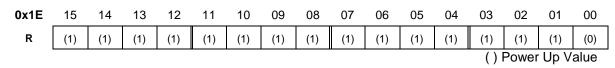

#### Subclass Register

Reads of this register return 0xFFFE. Writes to this register have no effect. The read contents are defined as follows:

| Bit(s) | Meaning                                                                       |

|--------|-------------------------------------------------------------------------------|

| 15     | This bit indicates that the V200 is a VXI <i>bus</i> defined Extended Device. |

| 14-0   | These bits indicate that this is an Extended Register Based Device.           |

## Suffix High Register

#### Suffix Low Register

These two registers are KineticSystems defined and hold the module's suffix. The suffix determines the particular option of the module. This information can be used to remotely establish available channel count, multibuffer options, etc. of the module. For further information on each option, refer to the Ordering Information section of this manual.

The module's suffix is always composed of four ASCII characters. The Suffix High register contains the first two characters; while, the last two characters are in the Suffix Low register. For instance, assume the module is a model V200-AA11. The module's suffix is "AA11". Converting this to ASCII yields 0x41413131.

For "user upgrades" write access to the Suffix registers may be obtained by moving strap STP8 to the ENA position. Strap STP8 must be returned to the DIS position when writing is complete.

**NOTE:** Special care must be taken while writing information into these locations. Once a register has been written, a minimum of 3ms must pass before any User Defined Register may be read or written.

## **User Defined Registers**

Offsets 0x24 through 0x3E are READ/WRITE registers and may be used to store user defined data. These registers are contained in non-volatile EEPROM.

**NOTE:** Special care must be taken while writing information into these locations. Once a register has been written, a minimum of 3ms must pass before any User Defined Register may be read or written.

## V200 Operational Registers, A32 Space

## Control/Status Register

The Control/Status Register is a write/read register located at an offset of 0x00 from the A32 base address of the V200 operational registers. This register is used to check various status indicators on the V200 and to enable or disable module functions. The following diagram shows the bit layout for the Control/Status Register.

| 0x00 | 31  | 30         | 29         | 28         | 27         | 26         | 25         | 24         | 23  | 22         | 21         | 20         | 19         | 18         | 17         | 16         |

|------|-----|------------|------------|------------|------------|------------|------------|------------|-----|------------|------------|------------|------------|------------|------------|------------|

| R/W  | (0) | (0)        | (0)        | (0)        | (0)        | (0)        | (0)        | (0)        | (0) | (0)        | (0)        | (0)        | (0)        | (0)        | (0)        | (0)        |

|      |     |            |            |            |            |            |            |            |     |            |            |            | ()         | Power      | Up V       | alue       |

|      | 15  | 14         | 13         | 12         | 11         | 10         | 09         | 08         | 07  | 06         | 05         | 04         | 03         | 02         | 01         | 00         |

| R/W  | (0) | GPB<br>STG | GPB<br>ARM | GPB<br>TRE | GPB<br>MBE | GPB<br>DSF | GPB<br>VXF | GPB<br>RUN | (0) | GPA<br>STG | GPA<br>ARM | GPA<br>TRE | GPA<br>MBE | GPA<br>DSF | GPA<br>VXF | GPA<br>RUN |

|      |     |            |            |            |            |            |            |            |     |            |            |            | ()         | Power      | Up V       | alue       |

| Bit(s) | Mnemonic | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|