# Model V207

16-bit, High-speed ADC Subsystem

## **User's Manual**

March 6, 2003

(C) 1998, 2001, 2002, 2003 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved This manual describes operation of current versions of the V207:

- V207-ZA13 Basic V207 unit: 16-bit, 500 ksamples/second ADC with Ping-Pong output buffer and 16-bit data transfer capability.

- V207-ZB13 Basic unit plus 1 Mbyte linear Multi-buffer with transient capture and 32bit data transfer capability.

- V207-ZB23 Basic unit plus 4 Mbyte linear Multi-buffer with transient capture and 32bit data transfer capability.

- V207-ZC13 Basic unit plus Digi-bus interface.

- V207-ZD23 Basic unit plus 4 Mbyte circular Multi-buffer with transient capture and 32-bit data transfer capability.

- V207-ZD33 Basic unit plus 16 Mbyte circular Multi-buffer with transient capture and 32-bit data transfer capability.

**Appendix A** describes operational differences between the V207-wByz and V207-wDyz units. **Appendix B** lists differences between earlier versions and current versions of some of the above models. The primary difference between version-2 (V207-...2) and version-3 (V207-...3) models is that the version-2 units only support 16-bit data transfer (D16) capability. Version-3 units support both D16 and D32 data transfer.

# **Table of Contents**

| About This Manual                                               | 1    |

|-----------------------------------------------------------------|------|

| Organization                                                    | 1    |

| Glossary                                                        |      |

| Chapter 1: Introduction                                         |      |

| •                                                               |      |

| About the V207                                                  |      |

| Getting Started                                                 |      |

| Unpacking the V207                                              | 4    |

| Chapter 2: Installation and Configuration                       | 5    |

| Setting the Logical Address Switches                            |      |

| Module Insertion                                                |      |

| Module Configuration                                            |      |

| -                                                               |      |

| Chapter 3: Understanding the V207/V208 Family                   |      |

| Overview                                                        |      |

| The MUX-bus                                                     |      |

| The V207 Family of Signal Conditioning and Multiplexing Modules | 8    |

| The Digi-bus                                                    | . 11 |

| Chapter 4: Understanding the V207                               | .13  |

| Overview                                                        | 13   |

| V207 Specifications.                                            |      |

| Setup Memories                                                  |      |

| Scan RAM                                                        |      |

| Limit Memory                                                    |      |

| Output Data Buffers                                             |      |

| Ping-Pong Memory                                                |      |

| Multi-buffer Memory Option                                      |      |

| Selecting the Sample Clock Source                               |      |

| Selecting the Sample Clock Rate                                 |      |

| Trigger Lines                                                   |      |

| Event Triggers                                                  |      |

| Timing Considerations in the V207                               |      |

| Synchronization of Multiple V207s                               |      |

| Interrupts                                                      |      |

| Front Panel                                                     |      |

| LEDs                                                            |      |

| SMB Connectors                                                  |      |

| Other Connectors                                                |      |

| V207 Adjustment procedure                                       |      |

|                                                                 |      |

| Chapter 5: Configuration and Operational Registers              |      |

| Address Space                                                   |      |

| Static and Dynamic Configuration                                |      |

| Communication Protocol                                          |      |

| Register Addressing                                             |      |

| Required Configuration Registers                                |      |

| ID Register 00h                                                 |      |

| Logical Address Register 00h                                    |      |

| Device Type Register 02h                                        |      |

| Status Register 04h                                             |      |

| Control Register 04h                                            |      |

| Offset Register 06h                                             |      |

| Additional Configuration Registers                              | . 36 |

| Attribute Register 08h<br>Serial Number Register 0Ah, 0Ch                                                                                                                                                                                                                                                                                                        |                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Serial Number Register 0Ah, 0Ch                                                                                                                                                                                                                                                                                                                                  |                            |

|                                                                                                                                                                                                                                                                                                                                                                  |                            |

| Version Number Register 0Eh                                                                                                                                                                                                                                                                                                                                      |                            |

| Reserved 10h, 12h, 14h, 16h, 18h                                                                                                                                                                                                                                                                                                                                 | 37                         |

| Interrupt Status Register 1Ah<br>Interrupt Control Register 1Ch                                                                                                                                                                                                                                                                                                  |                            |

| Interrupt Control Register 1Ch                                                                                                                                                                                                                                                                                                                                   |                            |

| Subclass Register 1Eh                                                                                                                                                                                                                                                                                                                                            |                            |

| Suffix Register 20h, 22h                                                                                                                                                                                                                                                                                                                                         | 40                         |

| User Defined Registers 24h - 3Eh                                                                                                                                                                                                                                                                                                                                 |                            |

| Operational Registers in A32 Space                                                                                                                                                                                                                                                                                                                               | 42                         |

| Sample Clock Register 00h                                                                                                                                                                                                                                                                                                                                        | 42                         |

| Trigger Register 1 (Front panel & Sample clock) 02h                                                                                                                                                                                                                                                                                                              | 43                         |

| Trigger Register 2 04h                                                                                                                                                                                                                                                                                                                                           |                            |

| Setup Register 06h                                                                                                                                                                                                                                                                                                                                               |                            |

| Channel Limit-Violation Register 08h                                                                                                                                                                                                                                                                                                                             |                            |

| Total Samples-Per-Frame Register (Digi-bus option) 10h                                                                                                                                                                                                                                                                                                           |                            |

| Samples-Per-Frame from this Source Register (Digi-bus option) 12h                                                                                                                                                                                                                                                                                                |                            |

| Start Address Register (Digi-bus option) 14h                                                                                                                                                                                                                                                                                                                     |                            |

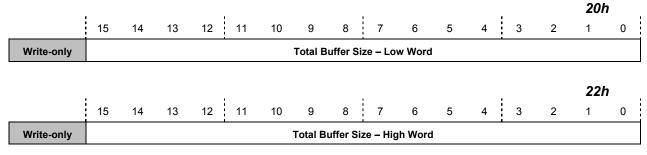

| Total Buffer-Size Register (Multi-buffer option) 20h, 22h                                                                                                                                                                                                                                                                                                        |                            |

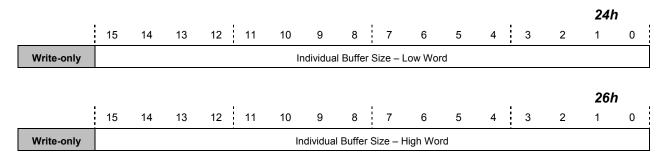

| Individual Buffer-Size Register (Multi-buffer option) 24h, 26h                                                                                                                                                                                                                                                                                                   |                            |

| Buffer-Full Flag Register (Multi-buffer option) 28h                                                                                                                                                                                                                                                                                                              |                            |

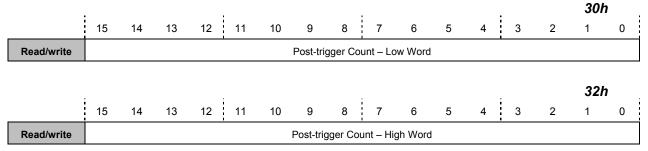

| Countdown Register (Multi-buffer transient option) 30h, 32h                                                                                                                                                                                                                                                                                                      |                            |

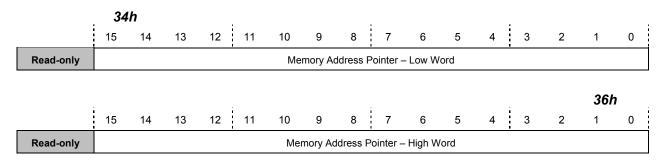

| Trigger Address Register (Multi-buffer transient option) 34h, 36h                                                                                                                                                                                                                                                                                                |                            |

| Scan RAM 200h - 3FEh                                                                                                                                                                                                                                                                                                                                             |                            |

| Limit Memory 400h - 5FEh                                                                                                                                                                                                                                                                                                                                         |                            |

| Ping-Pong Memory 600h - 7FEh                                                                                                                                                                                                                                                                                                                                     |                            |

| Multi-buffer Memory (optional)                                                                                                                                                                                                                                                                                                                                   | 54                         |

| Chapter 6: Programming Information                                                                                                                                                                                                                                                                                                                               | 56                         |

| Example procedures that use the Multi-buffer to capture transient data                                                                                                                                                                                                                                                                                           | 56                         |

| Appendix A: Differences between the V207–.B and the V207–.D                                                                                                                                                                                                                                                                                                      | 61                         |

| Introduction                                                                                                                                                                                                                                                                                                                                                     |                            |

| Setup Register (06h)                                                                                                                                                                                                                                                                                                                                             |                            |

| Buffer-Full Flag Register (28h)                                                                                                                                                                                                                                                                                                                                  |                            |

| Appendix B: Differences—Earlier versions                                                                                                                                                                                                                                                                                                                         |                            |

| Appendix C: Data Buffering Methods                                                                                                                                                                                                                                                                                                                               |                            |

| Introduction                                                                                                                                                                                                                                                                                                                                                     |                            |

| Ping-Pong Memory                                                                                                                                                                                                                                                                                                                                                 |                            |

| Multi-buffer Option                                                                                                                                                                                                                                                                                                                                              |                            |

| Digi-bus Option                                                                                                                                                                                                                                                                                                                                                  | 67                         |

| Acquiring Data from the Ping-Pong Memory                                                                                                                                                                                                                                                                                                                         |                            |

| Acquiring Data from the Multi-buffer Memory—Continuous Mode                                                                                                                                                                                                                                                                                                      |                            |

| Acquiring Data from the Multi-buffer Memory—Transient Mode                                                                                                                                                                                                                                                                                                       |                            |

|                                                                                                                                                                                                                                                                                                                                                                  |                            |

|                                                                                                                                                                                                                                                                                                                                                                  |                            |

| Appendix D: About KineticSystems                                                                                                                                                                                                                                                                                                                                 | ••••••                     |

|                                                                                                                                                                                                                                                                                                                                                                  |                            |

| Appendix D: About KineticSystems<br>The Leader in the Delivery of High-performance CAMAC-based Products                                                                                                                                                                                                                                                          | 71                         |

| Appendix D: About KineticSystems<br>The Leader in the Delivery of High-performance CAMAC-based Products<br>Innovation with the CAMAC Serial Highway                                                                                                                                                                                                              | 71<br>71                   |

| Appendix D: About KineticSystems<br>The Leader in the Delivery of High-performance CAMAC-based Products<br>Innovation with the CAMAC Serial Highway<br>H•TMS, a Turn-key Testing Solution, Added to Our Product Range                                                                                                                                            | 71<br>71<br>71             |

| <ul> <li>Appendix D: About KineticSystems</li> <li>The Leader in the Delivery of High-performance CAMAC-based Products</li> <li>Innovation with the CAMAC Serial Highway</li> <li>H•TMS, a Turn-key Testing Solution, Added to Our Product Range</li> <li>A Major Player in VXIbus, a Rapidly Growing Interface Standard</li> </ul>                              | 71<br>71<br>71<br>72       |

| <ul> <li>Appendix D: About KineticSystems</li> <li>The Leader in the Delivery of High-performance CAMAC-based Products</li> <li>Innovation with the CAMAC Serial Highway</li> <li>H•TMS, a Turn-key Testing Solution, Added to Our Product Range</li> <li>A Major Player in VXIbus, a Rapidly Growing Interface Standard</li> <li>KineticSystems Today</li></ul> | 71<br>71<br>71<br>72<br>72 |

| <ul> <li>Appendix D: About KineticSystems</li> <li>The Leader in the Delivery of High-performance CAMAC-based Products</li> <li>Innovation with the CAMAC Serial Highway</li> <li>H•TMS, a Turn-key Testing Solution, Added to Our Product Range</li> <li>A Major Player in VXIbus, a Rapidly Growing Interface Standard</li> <li>KineticSystems Today</li></ul> |                            |

# Table of Figures

| V207 Switch Locations         | 5                                       |

|-------------------------------|-----------------------------------------|

|                               |                                         |

| V241 Block Diagram            | 9                                       |

| V246 Block Diagram            |                                         |

| V252 Block Diagram            |                                         |

|                               |                                         |

| Digi-bus concept              | 12                                      |

| V207 block diagram            |                                         |

|                               |                                         |

|                               |                                         |

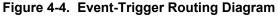

| Event-Trigger Routing Diagram | 23                                      |

|                               | V207 Switch Locations<br>MUX-bus timing |

# Table of Tables

| Table 4-1. | Performance Characteristics of the V207.                   |    |

|------------|------------------------------------------------------------|----|

| Table 4-2. | Maximum Number of Channels with Internal Sample Clock      |    |

| Table 4-3. | Interrupt Sources                                          | 25 |

|            | Relationship between the "m" Parameter and Required Memory |    |

| Table 5-2. | Sources of Interrupts                                      |    |

| Table 5-3. | Interrupt Request Levels                                   |    |

| Table 5-4. | Clock Sources                                              |    |

| Table 5-5. | Internal Sample Clock Frequency Selection                  |    |

| Table 5-6. | VXIbus Trigger Line Selection                              | 44 |

# **About This Manual**

# Organization

Chapter 1, *Introduction*, gives you a brief overview of the Model V207, lists items you need to get started, and explains how to safely unpack your module.

Chapter 2, *Installation and Configuration*, explains how to configure the V207 and correctly insert it into a C-size VXIbus mainframe.

Chapter 3, *Understanding the V207/V208 Family*, provides information about the V207, associated signal-conditioning modules, and interconnection methods.

Chapter 4, Understanding the V207, describes the performance of the V207.

Chapter 5, *Configuration and Operational Registers*, explains how to access and control the V207.

Chapter 6, *Programming Information*, gives you example setup procedures for preparing the V207 to acquire data.

The *Appendices* provide additional information that may be helpful in the use of the Model V207, in learning more about KineticSystems and its products, and in quickly reaching us.

# Glossary

Following is a glossary of some of the terms and conventions used throughout this manual:

| *                          | An indicator that a register bit contains low-true data. For example, writing a <b>"0"</b> to a bit labeled Enable* would cause a function to be enabled.                                                                                                        |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A16 Space                  | The first 64 kbytes of address space, accessible with 16-bit addressing. The configuration registers of VXI devices occupy 64-byte blocks of this address space. The Logical Address of a device determines which 64-block block is associated with that device. |

| A32 Space                  | The 4 Gbyte address space, accessible with 32-bit addressing. A module can request a block of this address space via information contained in its <i>Configuration</i> registers. <i>Operational</i> registers, if present, reside in this space.                |

| ADC Clock                  | The rate at which data is presented to the ADC for digitization. The ADC clock rate is also equal to the maximum rate of aggregate data throughput for all digitized channels.                                                                                   |

| Configuration<br>Registers | Setup registers located in A16 space. Some are mandatory; some are optional.                                                                                                                                                                                     |

| D16                        | A single 16-bit data transfer.                                                                                                                                                                                                                                   |

| D16 BLK                       | A block transfer of 16-bit words.                                                                                                                                                                                                                                                                                                                        |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D32                           | A single 32-bit data transfer. Not all Slot-0 controllers support <b>D32</b> .                                                                                                                                                                                                                                                                           |

| D32 BLK                       | A block transfer of 32-bit words. Not all Slot-0 controllers support D32 BLK.                                                                                                                                                                                                                                                                            |

| Device                        | One of 255 devices that a VXIbus system can support. The term is often used interchangeably with "module." The distinction is that a VXIbus module can consist of more than one device.                                                                                                                                                                  |

| Digi-bus™                     | A high-speed digital bus protocol developed by KineticSystems and implemented on the VXI Local Bus. The <b>Digi-bus</b> protocol allows an ADC to transmit digital data to DSP and memory devices at high speeds without external wiring.                                                                                                                |

| DSP                           | Digital Signal Processor. Usually refers to VXIbus devices that perform autonomous digital signal processing of digital data.                                                                                                                                                                                                                            |

| Dynamic<br>Addressing         | The VXIbus addressing mode in which the address of a device is stored in a write-able register. See also Static Addressing.                                                                                                                                                                                                                              |

| hexadecimal                   | A base-16 number. The suffix, "h," indicates that a number is hexadecimal.<br>For example, $1Ah = 26_{10}$ ; $FFh = 255_{10}$ ; $1000h = 4096_{10}$ .                                                                                                                                                                                                    |

| Local Bus                     | A user-definable 12-line bus implemented on the P2 connectors of the VXIbus.                                                                                                                                                                                                                                                                             |

| Logical<br>Address            | A VXIbus module's unique address. A VXIbus system has 254 logical addresses that are available. "0" is the address of the Slot-0 controller. "255" specifies that dynamic addressing be used to address that module.                                                                                                                                     |

| MUX-bus™                      | A four-channel analog bus protocol developed by Kinetic Systems and implemented on the VXI Local Bus. The <b>MUX-bus</b> protocol allows signal-conditioning modules to transmit analog data to an ADC module at high speeds with high accuracy without external wiring.                                                                                 |

| Operational<br>Registers      | Setup and data-transfer registers that are located in A32 address space.                                                                                                                                                                                                                                                                                 |

| RAM                           | Random Access Memory. RAM refers to a memory block that has direct addressable access, as opposed to sequential access.                                                                                                                                                                                                                                  |

| Resource<br>Manager           | Software that sets logical addresses and optimally configures Operational register addresses and memory-block addresses in a system. The manufacturer of the Slot-0 controller provides this software, often referred to as "RESMAN."                                                                                                                    |

| Sample Clock or<br>Scan Clock | The rate at which each channel is digitized. Each tick of the sample clock initiates digitization of the channels in the order defined in Scan RAM. Digitization occurs at the rate of the ADC clock. Note that, in this context, "sample" and "scan" are interchangeable, as in "sample clock" and "scan clock" or as in "sample rate" and "scan rate." |

| Static                        | The VXIbus addressing mode in which the address of a device is stored in a                                                                                                                                                                                                                                                                               |

|                               |                                                                                                                                                                                                                                                                                                                                                          |

Addressing switch register. See also Dynamic Addressing.

# **Chapter 1: Introduction**

# About the V207

The V207 is a single-width, C-size, register-based VXIbus module that provides high-speed, high-resolution, analog-to-digital conversion. This module is intended for use with VXIbus signal conditioning modules that incorporate the analog **MUX-bus** (models V241, V246, V252 and V253) to provide flexible system configurations without the need for inter-module cabling. The 96-channel MUX-bus compatible V243 is intended for use with the V208. It will operate with the high-speed V207, but with reduced accuracy.

The V207 provides four instrumentation amplifier inputs to increase throughput with large numbers of input channels. When used with appropriate signal-conditioning modules, up to 256 channels can be digitized. If no **MUX-bus** signal-conditioning modules are used, the V207 can digitize up to four preconditioned signals that connect to front-panel isolated BNC connectors. The V207 provides a high degree of flexibility for configuring analog sampling systems. With the optional Multi-buffer memory, data can fill the buffer at high sample rates and then be emptied in bursts over the VXIbus. Multi-buffers can be operated in *Continuous* or *Transient* modes. If the **Digi-bus** option is used, the digital data can stream to the V165 Digital Signal Processor, the V110 RAM memory module or to other modules supporting **Digi-bus** protocol. The V207 supports both static and dynamic configuration. Access to digitized data and to operational registers is via **A32** memory space. Data transfers use **D16** and **D32** protocol. The V207 is available with several digital-output options and Multi-buffer size options. The part number is V207-wxyz, where:

*w* specifies the sampling rate:

• Z = 500 ksamples/s

*x* selects the digital output option:

- A = Ping-Pong buffer

- B = Linear Multi-buffer with transient capture option without pre-trigger capability

- C = **Digi-bus**

- D = Circular Multi-buffer with transient capture option with pre-trigger capability

*y* specifies the Multi-buffer size:

- 1 = 1 Mbyte Multi-buffer

- 2 = 4 Mbyte Multi-buffer

- 3 = 16 Mbyte Multi-buffer

z specifies the version number.

Version 3 of a V207 with sampling rate to 500 ksamples/s and 16 Mbyte Multi-buffer with transient capture pre-trigger capability is specified as V207-ZD33, for example.

## **Getting Started**

To set up and use your V207 VXIbus module, you will need most or all of the following:

- The V207, configured with any appropriate options, and its User Manual

- One or more of the following **MUX-bus**-compatible signal-conditioning modules and their User Manuals:

- V241 96-channel, high-level, scanning MUX

- V246 8-channel bridge signal conditioner

- V252 8 or 16-channel, 8-pole analog filter

- V253 16-channel, programmable gain / analog filter

- One or more of the following software packages:

- VXI*plug&play* instrument driver(s)

- VISA software associated with a computer interface or Slot-0 controller that supports the VXI *plug&play* standards.

- LabVIEW for Windows

- LabWindows/CVI

- MS Visual Basic

- KSC *Reality* software

- "VXI Data Acquisition Handbook" by Dr. J. W. Tippie

- Your VXIbus system with its Resource Manager and high-level test and/or application software

## **Unpacking the V207**

The V207 comes in an anti-static bag to avoid electrostatic damage. Electrostatic discharge to the module can damage components on it. Please take the following precautions when unpacking the module:

- Ground yourself with a grounding strap or by touching a grounded object.

- Touch the anti-static package to a metal part of your VXIbus chassis before removing the module from the package.

- Remove the module from the package and inspect the module for damage.

- Do not install the module into the VXIbus chassis until you are satisfied that the module exhibits no obvious mechanical damage and is configured to conform to the desiring operating environment. The next chapter describes installation and configuration.

# **Chapter 2: Installation and Configuration**

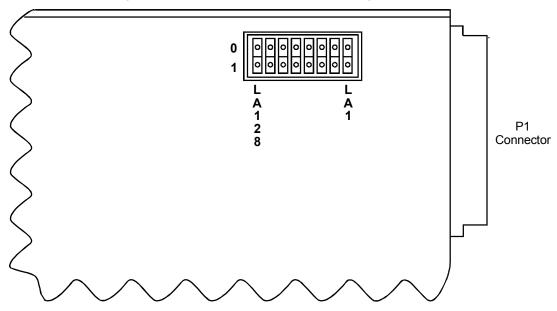

# **Setting the Logical Address Switches**

A VXI system can have as many as 255 devices, with each having a unique number in the range from zero to 254. Eight bits represent the number, which is the Logical Address of the device. VXIbus defines two concepts of addressing: "static" and "dynamic." All VXIbus devices *must* allow static addressing, in which the address is determined by the setting of a switch register. VXIbus devices may, but are not required to, support dynamic addressing. In dynamic addressing, the Logical Address is stored in a software-addressable register. For reasons discussed in Chapter 5, all KineticSystems VXIbus devices support dynamic as well as static addressing.

Before installing the V207 in the VXIbus chassis, you must set the switch register to an appropriate value. If you wish to employ static addressing you must make sure you set the switch register to a unique value other than 0 or 255. It is a good idea to note module addresses in an accessible log, because if you replace a module, it is very important that the new module have the same address as the replaced one.

If your system employs dynamic addressing, which delegates the task of assigning device addresses to the Resource Manager software, then make sure the address switch is set to 255 (all "1"s).

Note: To set a Logical Address bit to "1" depress the bottom segment of the switch.

Figure 2-1. V207 Switch Locations

## **Module Insertion**

Before inserting your VXIbus module into the chassis, make sure that the chassis is plugged into electrical power but *not turned on*. The power cord provides a ground connection for the mainframe and protects the equipment and you from electrical harm.

In a VXI system, the Bus Grant and IACK signals are received and transmitted by each of the modules. These signals must be jumpered around any vacant slots in the mainframe. Most

current mainframes, including our V194 and V195, contain jumperless backplanes, where the Bus Grant and IACK signals are automatically jumpered when a slot is empty.

If your mainframe does not contain a jumperless backplane, you must position certain jumpers correctly on the chassis backplane to assure that the V207 acknowledges interrupts properly. Remove the Interrupt Acknowledge (IACK) jumper from the slot selected for the V207 and install daisy-chain jumpers in any empty slots between the V207 and the Slot 0 Controller. You can now insert the V207 into the chassis. Slowly push it in until its plug connectors are resting against the backplane connectors. Then, using evenly distributed pressure, press the module straight in until it seats in the slot and the module front panel is even with the chassis front panel. Tighten the top and bottom screws.

You may now safely apply power to the V207.

## **Module Configuration**

You, or your software, must perform two types of module configuration. The first has to do with VXIbus-related items and involves communication with V207 *configuration* registers. The second deals with setting parameters related to data acquisition and involves communication with V207 *operational* registers.

VXIbus-related configuration includes setting the logical address, specifying the amount of memory space required, specifying where in memory the V207 registers and memory blocks are located, and setting interrupt levels.

When you configure the V207 for data-acquisition, you must select a sample-clock source and clock rate, load the scan list in Scan RAM, and perhaps define Multi-buffer or **Digi-bus** parameters.

VXIbus devices occupy system memory space. The configuration registers for each VXIbus device have 64 bytes of memory space in the upper 16 kbytes of the 64-kbyte **A16** memory space. Whether you set the 8-bit Logical Address statically in the switch register or dynamically in the Logical Address register, those eight bits determines the base address of the 64-byte block of memory as follows:

| <br>15 | 14 | 13 | 12 | 11 | 10     | 9      | 8 | 7 | 6 | 5 | 4 | 3  | 2   | 1 | 0 |

|--------|----|----|----|----|--------|--------|---|---|---|---|---|----|-----|---|---|

| 1      | 1  |    |    | L  | ogical | Addres | s |   |   |   |   | Of | set |   |   |

Each 64-byte block contains several registers that supply information about the module, such as the manufacturer, the module identifier (i.e., "207h"), its class (register-based or message-based), serial number, and the amount of memory space it requires.

In addition to A16 addressing, a VXIbus device can also support A24 or A32 addressing. If a Multi-buffer option is chosen, the V207 requires either 16 or 32 Mbytes of memory space. The V207 therefore supports A32 addressing since the maximum size of A24 memory is 16 Mbytes. The operational registers are all in A32 space. To access them, one must first write a proper offset value to the Offset register in A16 space. Refer to Chapter 5 for details relating to the *configuration* and *operational* registers.

# Chapter 3: Understanding the V207/V208 Family

# Overview

The V207 is a member of a versatile family of analog-to-digital converter (ADC) modules and signal conditioning modules. You can use from one to eleven signal-conditioning modules, in a VXIbus mainframe, with a single V207 or V208 scanning ADC module. The signal-conditioning modules transmit their analog data to the host ADC over the VXI Local Bus using **MUX-bus** protocol.

The V207 transmits its digitized data to a slot-0 controller via the VXIbus backplane *or* to one or more companion modules via the Local Bus using **Digi-bus** protocol. The flow of data is from right to left. Signal conditioning modules using **MUX-bus** protocol are positioned to the right of the ADC; slot-0 controllers and modules receiving digitized data using **Digi-bus** protocol are positioned to the left.

The V207 provides aggregate sampling rates to 500 ksamples/s. It supports up to 256 **MUX-bus** analog input channels. The V208 provides sampling rates to 100 or 200 ksamples/s. It supports up to 2048 **MUX-bus** channels.

The **MUX-bus** family of analog front-end modules includes:

- V241 96-channel multiplexer for high-level signals that do not require conditioning;

- V243 96-channel signal conditioner with programmable gain, programmable 2-pole active filters and precision calibration reference (V208 only);

- V246 **8-channel, bridge-input, signal conditioner** with programmable gain, programmable 6-pole filters, per-channel excitation source and optional simultaneous sampling;

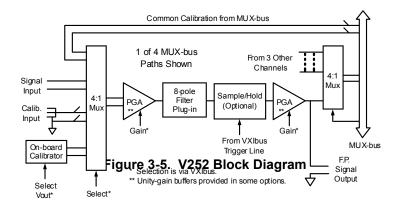

- V252 16-channel signal conditioner with factory-installed 8-pole filters, optional programmable gain and optional simultaneous sampling; and

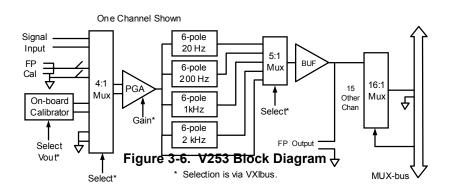

- V253 **16-channel signal conditioner** with programmable gain, optional 6-pole filters and optional simultaneous sampling.

You can "mix and match" these front-end modules with a single V207.

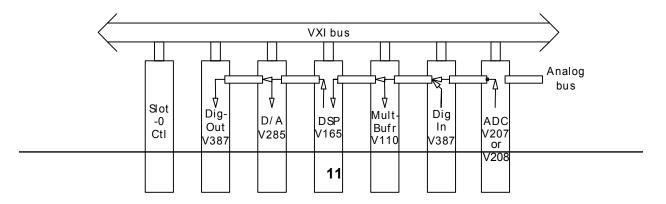

The **Digi-bus** family of modules includes:

- V110 RAM memory module with capacity to 128 Mbytes, on-board DSP for data manipulation, and programmable pre-trigger and post-trigger sample sizes for transient recorder applications;

- V165 TI 'C30-based DSP with 40 MFLOP processing power;

- V168 SHARC-based DSP with up to 1.44 GFLOP processing power;

- V285 **16-channel waveform generator** with programmable clock rates and programmable Bessel filters on each channel;

- V387 128-channel digital input/output module.

Data streams from the ADC to **Digi-bus** family modules over the VXI Local Bus using **Digi-bus** protocol and extends as far as adjacent modules in the VXIbus backplane propagate the bus. Brief descriptions of the **MUX-bus** and **Digi-bus** concepts and protocols follow.

# The MUX-bus

The **MUX-bus** is a four-channel, differential, analog bus implemented on the 12-line VXI Local Bus. Under control of the V207, signal-conditioning modules multiplex up to 256 analog signals onto the **MUX-bus**. The V207 provides the signals to start a new scan (or "frame") and to step to a new channel.

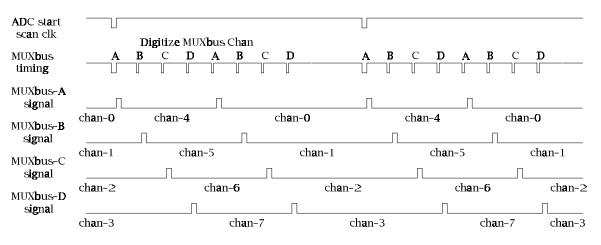

The **MUX-bus** operates as a four-phase bus to provide ample settling time before digitizing occurs. The four analog buses are referred to as A, B, C and D. Figure 3-1 below illustrates the **MUX-bus** cycle for an 8-channel system.

The V207 and its signal conditioning modules each contain a scan table called "Scan RAM." These tables contain the channel scanning order. On the signal-conditioning modules, channels 0, 4, 8, 12, etc., are associated with **MUX-bus** channel A. Channels 1, 5, 9, 13, etc., are associated with channel B, and so forth. The order of the channels in the scan list must be such that analog signals are presented to the **MUX-bus** channels in the order A, B, C, D, A, B, C, D, etc. In other words, the two least significant bits must follow the sequence 00, 01, 10, 11, 00, 01, etc. Other than this restriction, you can select any order of channel scanning that you wish within a group of signal conditioning modules on a common **MUX-bus**. An example of proper Scan RAM setup is given in the next chapter.

# The V207 Family of Signal Conditioning and Multiplexing Modules

A number of multiplexing and signal-conditioning modules use the **MUX-bus** protocol to connect to the V207 ADC. The family consists of the V241 high-level scanning multiplexer, the V246 bridge signal conditioner, and the V252 and V253 gain and filter modules. All are single-width, C-size, register-based VXIbus modules that support both static and dynamic addressing. The V243 low-level, low-noise module is intended for use with the V208.

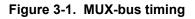

#### V241

The V241 acquires data economically from pre-conditioned channels and is intended for medium to high channel count applications with high-level signals ( $\pm$  10.24 V full scale). The V241 provides up to 96 high-level, differential input channels.

Two calibration channels are provided for each block of six input channels on a common multiplexer. One of each pair is internally set to analog ground (0 V differentially) while the other receives the **MUX-bus** system calibration voltage from the ADC card (+ 10 V differentially). This method allows end-to-end calibration of the V241 and V207.

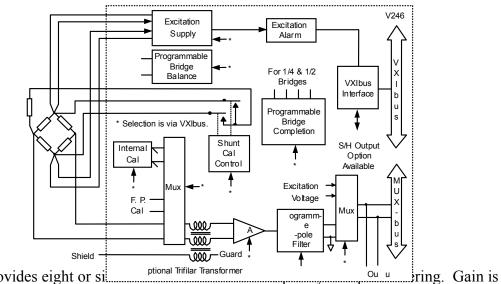

#### V246

The V246 provides eight channels of bridge signal conditioning. It accommodates transducers that represent one, two, or four active arms of a bridge circuit and permits the digitization of properly conditioned inputs from high-frequency strain gages, RTDs and other bridge-type sensors.

The V246 provides bridge completion, excitation, anti-aliasing filtering, and amplification for bridge-type inputs. It contains provisions for 2-point shunt calibration, automatic voltage and excitation calibration, as well as excitation alarms. A removable termination housing is available for convenient wiring of sensor leads.

Optional trifilar transformers are available for applications where high frequency electromagnetic interference is a concern. Simultaneous sampling is also an option.

#### V252

The V252 provides eight or significant transformer <u>ou u</u> ring. Gain is programmable on a channel-by-channel basis. You can select an eight-pole, low-pass, Bessel, Butterworth, Elliptic, or Constant-delay filter for each channel to provide high roll-off for excellent anti-alias filtering. Plug-in filter blocks provide cutoff frequencies that range from 10

#### Hz to 100 kHz.

Simultaneous sampling on all channels is available as an option. For calibration, the V207 provides a reference via the VXI Local Bus. An on-board reference can also provide a calibration input. The calibration signals can be applied to any channel.

#### V253

The V253 contains sixteen channels of programmable-frequency, low-pass filtering. Gain is programmable on a channel-by-channel basis as well. Options provide low-pass 6-pole Bessel or Chebyshev filters for all channels.

Simultaneous sampling on all channels is available as an option. Calibration inputs are provided via the front-panel connector, a mainframe reference from the **MUX-bus**, or from an on-board reference. A removable termination housing is available for convenient I/O wiring.

# The Digi-bus

In multi-channel systems, the V207 generates a digital stream of data with each tick of the sample clock. For applications that require further buffering and processing of the data, the **Digibus** option allows the digital data from the V207 to flow to other modules without being subject to the timing uncertainties of the VXI backplane.

Figure 3-7 illustrates the basic **Digi-bus** concept. The V207 is the source of the data stream and **Digi-bus** timing signals. The V387 digital input module can provide additional discrete data to the stream. The V110 memory module provides multi-buffered access to the data via the VXIbus. The data stream terminates at the V165 DSP, and the DSP software determines what passes on to the left. The V285 waveform generator and the V387 digital input/output module select items from the data stream for output.

The **Digi-bus** supports multiple data sources as well as multiple data sinks. The left-most module receiving digital data also must terminate the bus. The **Digi-bus** supports transfer rates up to 10 Mbytes/second.

The **Digi-bus** and Multi-buffer options are mutually exclusive. If you plan to use more than one V208 or V207 with **Digi-bus** output in the same mainframe, note that **Digi-bus** and MUX-bus use the VXIbus Local Bus. Therefore, if more than one ADC module has access to a **Digi-bus**, only an ADC module positioned at the right end of the **Digi-bus** group of modules can make use of the MUX-bus protocol.

Figure 3-7. Digi-bus concept

# Chapter 4: Understanding the V207

# Overview

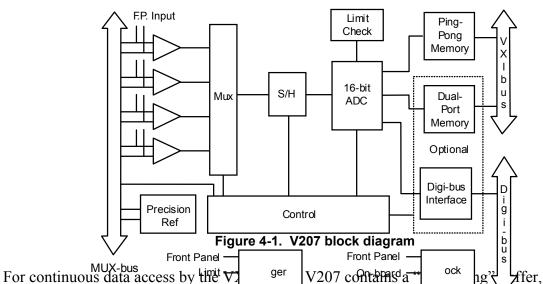

The V207 provides 16-bit analog-to-digital conversion at rates of 500 ksamples/s. It is used with signal-conditioning multiplexing modules that use the analog **MUX-bus** protocol to pass analog signals to the V207.

The V207 provides four differential inputs that allow high data throughput with large numbers of input channels connected via the **MUX-bus**. The V207 also accepts inputs via front-panel connectors. Note that you cannot use inputs from the **MUX-bus** and front-panel connectors at the same time.

For continuous data access by the  $\nabla 1$  ger V207 contains a pair of buffers each of which can hold 250 sixteen-bit words. During a scan, one buffer is being filled with ADC data from the multiplexed channels while the other contains the data from the previous scan and is available for readout from the VXIbus. At the start of the next scan, the roles of the buffers swap. The processor has one scan period to read the data from the V207. For example, if the scan clock rate is 100 Hz, the processor must recognize that the data is available and read it within 10 msec.

When the scan rate is above 100 Hz, the processor may be unable to respond quickly enough to empty the Ping-Pong buffer. The problem is that most operating system environments have worst-case latencies that are well over 1 ms. The solution is to use the **Digi-bus** to pass the data to a DSP or memory module; to use a large on-board buffer, a "multi-buffer," that can hold data from a number of scans and be read more efficiently with large DMA block transfers; or to use a Slot-0 controller, such as the V160 Grand Interconnect controller, with Multi-buffer option. The V207-<u>.D.</u> Multi-buffer option is available in two sizes: 4 Mbytes and 16 Mbytes. You use the operational registers in **A32** address space to specify the size of the buffer most suitable for your application and to divide the buffer into a number of segments. The ADC treats the memory buffer as a circular buffer. That is, when it reaches the end it resets its address to the start of the buffer. When the ADC fills a segment, the Multi-buffer sets a "segment-full" flag

and signals the user application with an interrupt. The operating system responds and reads data from the filled segment(s) while the ADC is filling a subsequent segment.

An important feature of a V207 with a Multi-buffer is *transient capture* mode. Transient capture refers to the ability of this module to store a block of data related to an "event" in its local Multibuffer, and then transmit that data over VXIbus, 32 bits at a time. When this mode is activated, a V207-.D.. begins recording its data into the circular Multi-buffer. The size of the buffer and the number of pre-trigger and post-trigger samples are programmable. The V207 can receive a trigger from its front-panel *Trigger In* connector or a VXIbus trigger line, or it can be triggered from software. Once triggered, it begins post-trigger and post-trigger samples—can be read via VXIbus. Therefore, VXIbus and host-computer transfer rates are not limiting factors when using this mode. Data storage can be at the maximum rate for the V207, with the recording time only limited by the size of the Multi-buffer.

If the **Digi-bus** option is present, the V207 acts as data source and "master" for the **Digi-bus**. It determines the **Digi-bus** clocking time, which relates to the ticks of the ADC conversion clock. It also provides a data "frame" signal, which is equivalent to the scan period. The **Digi-bus** is intended for use in continuous, rather than transient, data-taking applications.

# V207 Specifications

| Item                                   | Specifications                                                         |

|----------------------------------------|------------------------------------------------------------------------|

| Input Channels                         |                                                                        |

| Number                                 | 4, expandable to 256 via the MUX-bus                                   |

| Source                                 | Front-panel or MUX-bus on the P2 connector                             |

| Analog Signal Input Type               | Differential                                                           |

| Analog Input Range                     | ± 10.24 V                                                              |

| Input Impedance                        | Greater than 20 M $\Omega$                                             |

| Large Signal Analog Bandwidth (- 3 dB) | Greater than 100 kHz                                                   |

| Resolution                             | 16 bits, monotonic over operating temperature range                    |

| DC Accuracy                            | 0.02% FSR (FSR = 20.48 volts)                                          |

| Differential non-linearity             | 0.006% of FSR                                                          |

| Integral linearity                     | 14 bits                                                                |

| No missing codes                       | Guaranteed                                                             |

| Dynamic Performance                    |                                                                        |

| Maximum conversion rate                | 500,000 samples/second                                                 |

| Cross-talk                             | -70 dB                                                                 |

| Sample Clock                           |                                                                        |

| Internal source                        | Derived from the VXIbus precision 10 MHz clock                         |

| Frequency choices                      | 12 steps from 100 Hz to 500 kHz (1, 2, 5 sequence)                     |

| External source                        | TTL signal to 500 kHz                                                  |

| Duty cycle                             | 45 to 55%                                                              |

| Backplane source                       | 1 of 8 trigger lines on the VXIbus P2 connector                        |

| External Trigger                       |                                                                        |

| Source                                 | Negative-going TTL signal                                              |

| Minimum value                          | 50 nsec                                                                |

| Limit Checking                         | Level, $\pm$ slope                                                     |

| Resolution                             | 8 bits                                                                 |

| Maximum value                          | ± 10.16 V                                                              |

| Calibration                            | Precision 10 V reference on board, bussed to adjacent signal           |

| Front man al Orange stars              | conditioning modules via the <b>MUX-bus</b> for end-to-end calibration |

| Front-panel Connectors                 | BNCs and SMBs                                                          |

| Power Requirements                     |                                                                        |

| +5 V                                   | 3.2 A without Multi-buffer, 4.65 A with Multi-buffer                   |

| -5.2 V                                 | 40 mA                                                                  |

| +24 V<br>-24 V                         | 130 mA<br>130 mA                                                       |

| Environmental and Mechanical           |                                                                        |

| Temperature range                      |                                                                        |

| Operational                            | 0° C to + 50° C                                                        |

| Storage                                | -25° C to + 75° C                                                      |

| Relative humidity                      |                                                                        |

| Cooling requirements                   | 0 to 85%, non-condensing to 40° C                                      |

| Dimensions                             | 10 CFM<br>340 mm x 233 35 mm x 30 48 mm (C sized \/XIbus card)         |

| Front-panel potential                  | 340 mm x 233.35 mm x 30.48 mm (C-sized VXIbus card)                    |

|                                        | Chassis ground                                                         |

# **Setup Memories**

## Scan RAM

You can multiplex up to 256 analog-input channels into the V207. The contents of the scan memory (called "Scan RAM") determine the sampling sequence of the channels, and you must write the desired sequence into the 256-word Scan RAM before acquisition can begin. As each channel is converted, an address register increments, and the next location in Scan RAM selects the channel to be digitized. The same address register routes the converted data to the appropriate sequential location in Ping-Pong, Multi-buffer, or **Digi-bus** memory. Scan RAM exists in *all* **MUX-bus** modules. You must write the *same* sampling sequence into each Scan RAM, with an important exception. You must set bit 14 to a "1" in a module's scan RAM to indicate when the sequence applies to that particular module. In other words, when bit 14 is set, that module gates its selected analog signal onto the **MUX-bus**. Obviously, you must take care to not set bit 14 in more than one signal-conditioning module at the same address location.

Following is an example of loading the Scan RAM for the following module configuration:

- One V207 host ADC module and two V246 8-channel bridge signal conditioning modules.

- All 8 channels in each V246 are included in the scan list.

- V246 #1 is to be first in the list, followed by V246 #2.

- The channels in each V246 are to be scanned in order, 1 through 8.

The organization of the Scan RAM is as follows:

- Bit 15 is set to "1" to define the end of the list.

- Bit 14 is set to "1" in a signal conditioning module to connect a channel in *that module* to the **MUX-bus** at that point in the scan list.

- Bits 13 and 12 are not used in any Scan RAM and should be written as "0."

- Bits 11 through 0 define the channel to be scanned.

- Bits 1 and 0 *also* define the **MUX-bus** channel (A, B, C or D) being used.

- Bits 14 through 2 are ignored in the V207 ADC. Only the end-of-list flag (bit 15) and the **MUX-bus** channel selection (bits 1 and 0) are used in the V207's Scan RAM.

The Scan RAM setup considerations are:

- Bit 14 must be set to "1" in *only one* signal conditioning module at any Scan RAM address. Otherwise, more than one signal conditioning module will be connected to the MUX bus at the same time. This error will cause an "overlap" indication in one or more signal conditioning modules.

- Four **MUX-bus** channels are used to provide sufficient data settling time. If a sequence other than A, B, C, D (as defined by the two least significant bits in the channel address) is used, this sequence must be repeated throughout the scan list to produce predictable results. This also means that the number of channels in a scan list must be divisible by 4 (4, 8, 12, 16, etc.).

- The end-of-list flag (bit 15 = "1") must be in the same list location in the ADC and in all signal conditioning modules connected to it. This flag is placed in the list location that represents the last channel scanned in the scan list.

- There are many bits that are ignored in the V207's Scan RAM, and the channel address bits related to one signal conditioning module are ignored by others in the subsystem. However, a recommended convention is to write the same data pattern for bits 13-0 in the Scan RAM for the ADC and all signal conditioning modules, while writing "0" for bit 14 for all locations in the V207 Scan RAM and the appropriate values for bit 14 in the signal conditioning Scan RAM memories.

- All Scan RAM data is ignored for addresses beyond that which contains the end-of-list flag. Good convention would have those data words written with all "**0**'s."

- When using multibuffer memory, only an even number of channels is allowed.

The following charts show the bit patterns to be written in the Scan RAM memories for this V207-V246 example:

| Address | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Data  | MUX | Selection |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|-------|-----|-----------|

| 200h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000h | А   |           |

| 202h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0001h | В   |           |

| 204h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0002h | С   |           |

| 206h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0003h | D   |           |

| 208h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0004h | А   |           |

| 20Ah    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0005h | В   |           |

| 20Ch    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0006h | С   |           |

| 20Eh    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0007h | D   |           |

| 210h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000h | А   |           |

| 212h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0001h | В   |           |

| 214h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0002h | С   |           |

| 216h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0003h | D   |           |

| 218h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0004h | А   |           |

| 21Ah    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0005h | В   |           |

| 21Ch    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0006h | С   |           |

| 21Eh    | 1  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 8007h | D   | End List  |

| 220h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000h |     |           |

|         | •  | •  | •  | •  | •  | •  | • | • | • | • | • | • | • | • | • | • |       |     |           |

| 3Feh    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000h |     |           |

#### Scan RAM - V207 ADC

#### Scan RAM - V246 Signal Conditioner #1

|         |    |    |    |    |    |    |   |   |   | • |   |   |   |   |   |   |       |     |           |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|-------|-----|-----------|

| Address | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Data  | Mux | Selection |

| 100h    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 4000h | А   | Channel 1 |

| 102h    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 4001h | В   | Channel 2 |

| 104h    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 4002h | С   | Channel 3 |

| 106h  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 4003h | D | Channel 4 |

|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------|---|-----------|

| 108h  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 4004h | А | Channel 5 |

| 10Ah  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 4005h | В | Channel 6 |

| 10Ch  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 4006h | С | Channel 7 |

| 10Eh  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 4007h | D | Channel 8 |

| 110h  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0000h | А |           |

| 112h  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0001h | в |           |

| 114h  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0002h | С |           |

| 116h  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0003h | D |           |

| 118h  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0004h | А |           |

| 11Ah  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0005h | в |           |

| 11Ch  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0006h | С |           |

| 11Eh  | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 8007h | D | End List  |

| 120h  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000h |   |           |

|       | • | • | ٠ | • | • | • | • | • | • | ٠ | ٠ | • | • | ٠ | ٠ | • |       |   |           |

| 10Feh | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000h |   |           |

Scan RAM - V246 Signal Conditioner #2

| Address | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Data  | Mux | Selection            |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|-------|-----|----------------------|

| 100h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000h | А   |                      |

| 102h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0001h | В   |                      |

| 104h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0002h | С   |                      |

| 106h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0003h | D   |                      |

| 108h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0004h | А   |                      |

| 10Ah    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0005h | В   |                      |

| 10Ch    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0006h | С   |                      |

| 10Eh    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0007h | D   |                      |

| 110h    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 4000h | А   | Channel 1            |

| 112h    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 4001h | В   | Channel 2            |

| 114h    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 4002h | С   | Channel 3            |

| 116h    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 4003h | D   | Channel 4            |

| 118h    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 4004h | А   | Channel 5            |

| 11Ah    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 4005h | В   | Channel 6            |

| 11Ch    | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 4006h | С   | Channel 7            |

| 11Eh    | 1  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | C007h | D   | Channel 8 + End List |

| 120h    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000h |     |                      |

|         | •  | •  | •  | •  | •  | •  | • | • | • | • | • | • | • | • | • | • |       |     |                      |

| 10Feh   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000h |     |                      |

## Limit Memory

You can assign to each channel a unique limit value that is stored in Limit Memory as an eight bit digital count and a slope bit. The eight bits correspond to the eight most significant bits of the converted data word. As the V207 digitizes each channel, the value is checked to see if the limit is exceeded. If it is, it asserts a VXIbus interrupt if Global Limit Enable—bit 3 in the Setup register—is enabled. A VXIbus trigger line is also asserted if Limit Enable—bit 11 in Trigger Register 2—is asserted. You can route this event trigger *from* the VXIbus trigger line to the front-panel Trigger Out connector, if you desire.

# **Output Data Buffers**

## Ping-Pong Memory

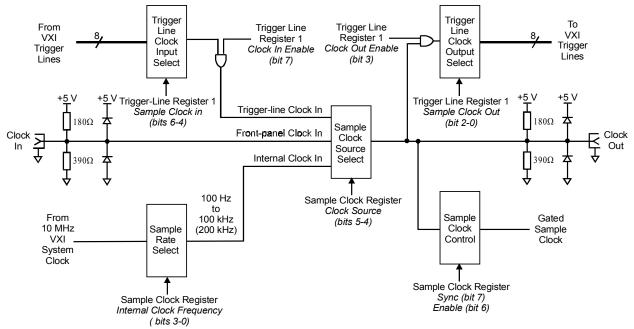

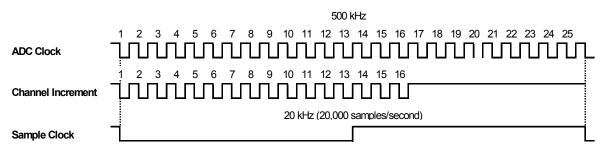

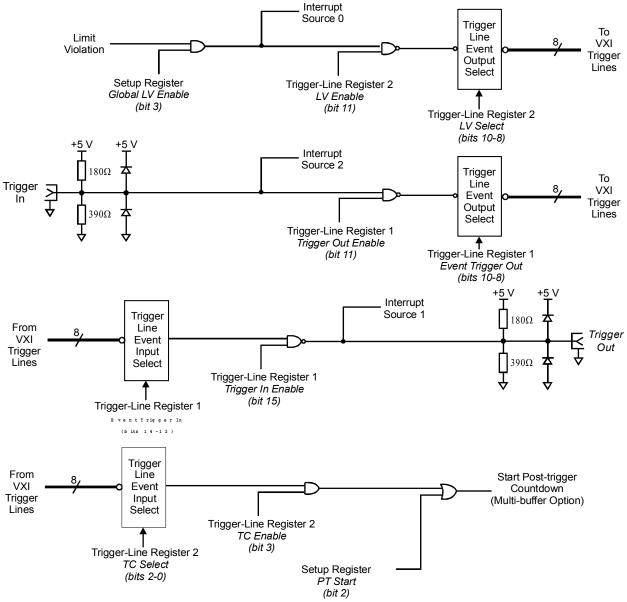

Between ticks of the sample clock, the ADC converts one 16-bit data point each from the list of active channels in Scan RAM. The number of words generated between each clock tick can be as high as 256 in the V207. System design must address how to transfer the data to external storage before the ADC overwrites it with subsequent conversions. Some form of buffering is usually needed since required sample rates may prohibit the processor from keeping up on a conversion-by-conversion basis.