128-Channel, Discrete I/O

# **Instruction Manual**

July, 2003

(C) 1994, 1995, 1996, 1997, 1998, 2001, 2003 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

# CONTENTS

| GENERAL DESCRIPTION                                                  | 4  |

|----------------------------------------------------------------------|----|

| FEATURES                                                             | 4  |

| SPECIFICATIONS                                                       | 5  |

| ORDERING INFORMATION                                                 | 8  |

| GETTING STARTED                                                      | 7  |

| INTRODUCTION                                                         | 9  |

| VXI Trigger Lines                                                    |    |

| System Configuration Validation                                      |    |

| Digi-bus                                                             |    |

| UNPACKING AND INSTALLATION                                           |    |

| Logical Address Switches                                             | 15 |

| Module Insertion                                                     |    |

| FRONT PANEL INFORMATION                                              | 16 |

| LEDs                                                                 | 16 |

| CONNECTORS                                                           |    |

| Mezzanine Card Front Panel Pinouts                                   | 19 |

| PROGRAMMING INFORMATION                                              | 24 |

| VMEbus/VXIbus Addressing                                             | 24 |

| VXIbus Configuration Registers                                       | 24 |

| Operational Registers                                                | 32 |

| V387 EXAMPLE: SETUP V387 TO SOURCE DATA ONTO DIGI-BUS ON VXI TRIGGER | 55 |

| DESCRIPTION OF OPTIONAL CARDS                                        |    |

| 16-Channel Isolated Input 5VDC                                       |    |

| 16-Channel Isolated Input 12VDC                                      | 56 |

| 16-Channel Isolated Input 24VDC                                      | 56 |

| 16-Channel Isolated Input 48VDC                                      |    |

| 16-Channel Isolated Input 120VAC                                     |    |

| 16-Channel Isolated Input 16VDC                                      |    |

| 16-Channel Isolated Input 28VDC                                      |    |

| 16-Channel Isolated Output                                           |    |

| 16-Channel Reed Relay Output                                         |    |

| 16-Channel Form "C" Relay Output                                     |    |

| 16-Channel AC Switch                                                 |    |

| 32-Channel TTL Input/Output                                          |    |

| 16-Channel Differential Input/Output                                 |    |

| Local Bus Data/Frame Source                                          |    |

| Local Bus Data Sink                                                  |    |

| APPENDIX B: V387 BOARD DRAWINGS                                      | 68 |

|                                                                      |    |

# LIST OF FIGURES

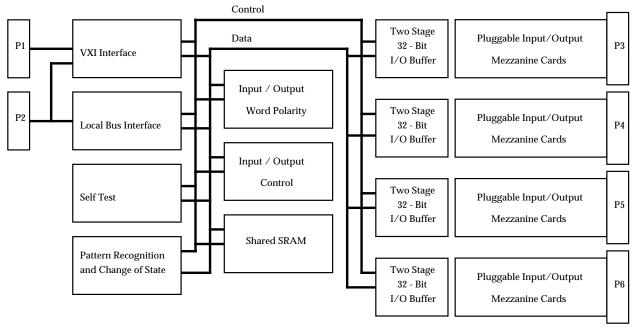

| FIGURE 1 - V387 BLOCK DIAGRAM        | 6    |

|--------------------------------------|------|

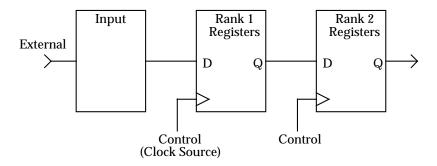

| FIGURE 2 - INPUT REGISTER DIAGRAM    | .12  |

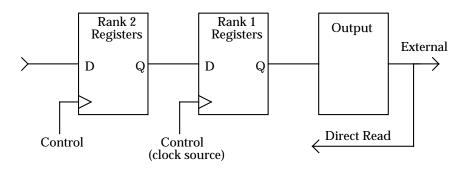

| FIGURE 3 - OUTPUT REGISTER DIAGRAM   | .13  |

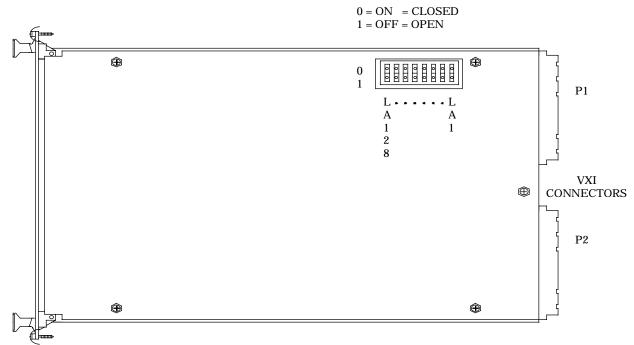

| FIGURE 4 - V387 SWITCH LOCATIONS     | .15  |

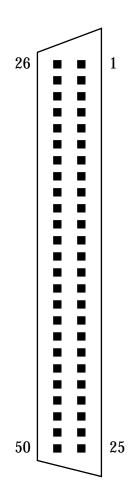

| FIGURE 5 - 50-POSITION SCSI-II PLUG  | .17  |

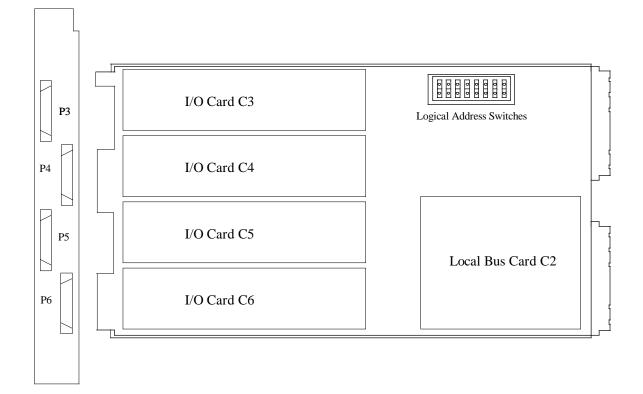

| FIGURE 6 - V387 CARD OUTLINES        | . 18 |

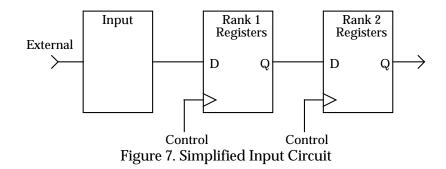

| FIGURE 7 - SIMPLIFIED INPUT CIRCUIT  | .57  |

| FIGURE 8 - SIMPLIFIED OUTPUT CIRCUIT | . 58 |

### LIST OF TABLES

| TABLE 1. ISOLATED INPUT CARDS    | 19 |

|----------------------------------|----|

| TABLE 2. ISOLATED OUTPUT CARDS   | 20 |

| TABLE 3. RELAY OUTPUT CARD       | 21 |

| TABLE 4. BI-DIRECTIONAL TTL CARD | 22 |

| TABLE 5. DIFFERENTIAL CARD       | 23 |

| TABLE 6. CONFIGURATION REGISTERS | 25 |

| TABLE 7. CHANNEL DEFINITIONS     |    |

| TABLE 8. OPERATIONAL REGISTERS.  |    |

| TABLE 9. DEBOUNCE TIME CONTROL   |    |

|                                  |    |

# **128 - channel Discrete Input/Output**

#### **GENERAL DESCRIPTION**

The V387 is a single-width, C-size VXIbus module that contains up to 128 channels of discrete input and/or output. The module is configurable on a 32-channel basis through four interchangeable mezzanine cards, which are available in an assortment of I/O options.

Three different mezzanine card types can be used. For bidirectional transfers, a non-isolated TTL version is available. Five isolated voltage options (TTL, 12VDC, 24VDC, 48VDC, and 120VAC), configured for either input or output signaling, are also available. Input isolation is achieved by using LED/photo-transistor optical isolators. Each option has 16 circuits with identical input voltage ratings, and the switching threshold is approximately ½ the rated input voltage. Each circuit draws more than five, but less than 15 milliamperes. The logic convention is such that a contact closure (voltage present) is interpreted as a logical "1". Each input is conditioned by filtering after the optical isolator. The filter time constant is programmable from 4 microseconds to over a second in 64 steps.

Output-only cards are available, with output circuits composed of reed relays, optical isolators, isolated ac switches, or single-pole, double-throw (Form "C") contacts. Each output card is a 16-channel circuit.

Input/output data is controlled in a 16-bit basis. Double buffering of I/O data allows the module to simultaneously sample or update all inputs or outputs, respectively. These actions are programmable for each card an may be initiated by selecting either a trigger line or one of four external sources. The module may be used with or without external handshake circuitry. The logical sense of the external handshake signals is programmable for each mezzanine card. The logical sense of each I/O word can also be set under program control. Pattern recognition capabilities are programmable in 16-bit increments. A pre-written data pattern, and a corresponding "enable" mask, are compared with the incoming data on a continuing basis. A change-of-state indicator is also updated on a continuing basis. Either function (pattern recognition or change-of-state) can be used to generate a VXIbus trigger or an interrupt. The selection of interrupt level and/or trigger line is made under program control.

An extensive Self-test is automatically performed on power-up. It can also be initiated by software. Module functionality as well as the I/O capability of each data byte is tested. A Pass/Fail status as well as problem source are indicated.

The V387 supports both static and dynamic configuration capabilities. Access to the data is through memory locations indicated by the Offset Register within the VXIbus Configuration Register set, using A32/A16, D16/D32 data transfers.

# **V387**

#### FEATURES

- 128 channel I/O capability in 32-channel increments

- Double buffered I/O data

- Pluggable mezzanine cards with various I/O options

- Trigger generation or interrupt on pattern recognition or change-of-state detection

- Programmable contact bounce suppression on inputs

- Variety of I/O strobe or handshake options

- Register-based

- Self-test capability

| SPECIFICATIONS                                                                                                             |                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Number of Channels                                                                                                         | 128 (maximum)                                                                                                                         |

| <b>Bidirectional I/O</b><br>Number of channels per circuit<br>I/O lines overvoltage protected and TTL pull-ups<br>provided | 32 TTL level signals                                                                                                                  |

| Input current draw<br>Input switching threshold                                                                            | greater than five, less than 10 milliamperes                                                                                          |

| "0" Level "1" Level<br>Output switching threshold<br>"0" Level "1" Level                                                   | <ul><li>1.5 volts maximum</li><li>3.5 volts minimum</li></ul>                                                                         |

| Low-level output current<br>High-level output current                                                                      | <ul> <li>0.7 volts maximum</li> <li>2.0 volts minimum</li> <li>-24 milliamperes, maximum</li> <li>10 milliamperes, maximum</li> </ul> |

| Input-Only Circuits                                                                                                        |                                                                                                                                       |

| Number of channels per circuit<br>Input signal options                                                                     | 16 two-wire, floating inputs<br>5, 12, 24, or 48 volts DC; 120 volts AC; Contact closure<br>(See ORDERING INFORMATION)                |

| Input isolation                                                                                                            | 500 volts                                                                                                                             |

| Input current draw<br>Switching threshold                                                                                  | greater than five, less than 15 milliamperes<br>approximately ½ rated input                                                           |

| Input filter time constant                                                                                                 | programmable from 4 microseconds to 480 seconds in 64 steps                                                                           |

| Output-Only Circuits                                                                                                       |                                                                                                                                       |

| Number of channels per circuit                                                                                             | 16                                                                                                                                    |

| Reed Relay option                                                                                                          |                                                                                                                                       |

| Maximum open-circuit voltage                                                                                               | 100 volts DC                                                                                                                          |

| Maximum current                                                                                                            | 0.5 amperes                                                                                                                           |

| Maximum switched load                                                                                                      | 10 volt-amperes                                                                                                                       |

| Life expectancy                                                                                                            | 5×10 <sup>6</sup> operations (with proper contact protection)                                                                         |

| Contact Resistance                                                                                                         | 200 mΩ, minimum                                                                                                                       |

| Operate time                                                                                                               | 330 microseconds, maximum                                                                                                             |

| Release time                                                                                                               | 150 microseconds, typical                                                                                                             |

| Insulation resistance                                                                                                      | 100 M $\Omega$ , minimum                                                                                                              |

| Output polarity                                                                                                            | Either                                                                                                                                |

| Contact bounce                                                                                                             | 3 milliseconds                                                                                                                        |

| Optical Isolator option                                                                                                    |                                                                                                                                       |

| Maximum open-circuit voltage                                                                                               | 30 volts                                                                                                                              |

| Maximum ON current                                                                                                         | 10 milliamperes                                                                                                                       |

| ON voltage drop                                                                                                            | 1 volt                                                                                                                                |

| OFF current                                                                                                                | Less than one microampere                                                                                                             |

| Output polarity                                                                                                            | Collector positive, with respect to Emitter                                                                                           |

| AC Switch option<br>Zero voltage turn-on                                                                                   |                                                                                                                                       |

| Zero voltage turn-on<br>Maximum open-circuit voltage                                                                       | 10 volts, peak                                                                                                                        |

| Maximum Open-circuit voltage<br>Maximum ON current                                                                         | 250 VRMS (400 VPeak)                                                                                                                  |

| Minimum ON current                                                                                                         | 1 ampere, 47 to 70 hertz                                                                                                              |

| ON voltage drop                                                                                                            | 0.01 amperes                                                                                                                          |

| Turn-on time (60 Hertz)                                                                                                    | 1.6 VRMS, maximum (at rated current)                                                                                                  |

| Turn-off time (60 Hertz)                                                                                                   | 8.3 milliseconds, maximum                                                                                                             |

| Form "C" Relay option                                                                                                      | 8.4 milliseconds, maximum                                                                                                             |

| Maximum open-circuit voltage                                                                                               | 500 VDC/130 VAC                                                                                                                       |

| Maximum open chedit voltage                                                                                                | 1 ampere, switched or carry                                                                                                           |

| Maximum switched load                                                                                                      |                                                                                                                                       |

| Life expectancy                                                                                                            | 50 volt-amperes                                                                                                                       |

| Contact Resistance                                                                                                         | $5 \times 10^9$ operations (with proper contact protection)                                                                           |

| Operate time                                                                                                               | 100 m $\Omega$ , max; stable to within ±10% over life                                                                                 |

| Release time                                                                                                               | 2.3 milliseconds, typical                                                                                                             |

| Breakdown voltage                                                                                                          | 1.5 milliseconds, maximum                                                                                                             |

| Dicardown voltage                                                                                                          | 500 volts peak                                                                                                                        |

| Model V387-ZA11       |                 |

|-----------------------|-----------------|

| Insulation resistance | 100 MΩ, minimum |

| Connector Type               | ** TBD **                                   |

|------------------------------|---------------------------------------------|

| Mating Connector             | KineticSystems Model ** TBD **              |

| Power Requirements           |                                             |

| +5 volts                     | ** TBD **                                   |

| +24 volts                    | ** TBD **                                   |

| Environmental and Mechanical |                                             |

| Temperature Range            |                                             |

| Operational                  | 0 to +50°C                                  |

| Storage                      | -25°C to +75°C                              |

| Relative Humidity            | 0 to 85%, non-condensing to 40°C            |

| Cooling Requirements         | 10 cubic feet per minute                    |

| Dimensions                   | 340mm X 233.35mm X 30.48mm (C-sized VXIbus) |

| Front Panel Potential        | Chassis Ground                              |

#### Model V387-ZA11 ORDERING INFORMATION

| Model V387-ZA11 | 128-Channel Discrete Input/Output Base Board    |

|-----------------|-------------------------------------------------|

| Model P300-300A | 16-Channel Isolated Input Mezzanine Card 5VDC   |

| Model P300-301A | 16-Channel Isolated Input Mezzanine Card 12VDC  |

| Model P300-302A | 16-Channel Isolated Input Mezzanine Card 24VDC  |

| Model P300-303A | 16-Channel Isolated Input Mezzanine Card 48VDC  |

| Model P300-304A | 16-Channel Isolated Input Mezzanine Card 120VAC |

| Model P300-341A | 16-Channel Isolated Output Mezzanine Card       |

| Model P300-342A | 16-Channel Reed Relay Output Mezzanine Card     |

| Model P300-343A | 16-Channel Form "C" Relay Output Mezzanine Card |

| Model P300-344A | 16-Channel AC Switch Mezzanine Card             |

| Model P300-380A | 32-Channel TTL Input/Output Mezzanine Card      |

| Model P500-387A | Local Bus Data/Frame Source Mezzanine Card      |

| Model P500-387A | Local Bus Data/Frame Source Mezzanine Card      |

| Model P501-387A | Local Bus Data Sink Mezzanine Card              |

|                 |                                                 |

FIGURE 1 - V387 BLOCK DIAGRAM

#### **Getting Started**

This manual is organized into four sections:

- The *Introduction* section describes the capabilities of the V387.

- The Unpacking and Installation section explains how to install the V387 into a VXI chassis.

- The *Programming Information* section explains how to access and control the V387. The first half of the section explains the use of the Configuration Registers. These general purpose registers are standard registers defined by VXI which are used to identify the module and control interrupts. The second half of the section explains the use of the Operational Registers. The registers are specific for operation and control of the V387. These registers are used to control pattern matching, TTL trigger lines, I/O data, etc.

- The *Appendix* provides additional information about specific I/O mezzanine cards.

The following is a list of some of the terms used throughout this manual:

| A16 Space: | As described in the VXI specification, this mnemonic is used to describe the first 64   |

|------------|-----------------------------------------------------------------------------------------|

|            | kilobytes of address space. Every VXI module is automatically allocated a 64 byte       |

|            | block of this address space (also known as Configuration Registers). The exact location |

|            | is determined by the logical address of the module.                                     |

A32 Space: As described in the VXI specification, this mnemonic is used to describe the 4 Gigabyte block of address space provided. Any module can request a block of this address space from information contained in its Configuration Registers. This memory block is also called the Operational Registers.

Configuration

Registers: See A16 Space.

- D16: As described in the VXI specification, this mnemonic is used to describe a single 16-bit data transfer.

- D32: As described in the VXI specification, this mnemonic is used to describe a single 32-bit data transfer. This mode is not supported by all Slot-0 controllers. Check the owners manual for the Slot-0 before attempting this type of transfer.

- I/O Word: This term is used to designate which of the eight 16-bit input/output words is being referenced. I/O Word numbers range from 0 to 7 and represent channels 1 to 128 in 16-channel groups. See Table 7.

| Logical<br>Address:       | Every VXI module is given a unique logical address. There are a total of 256 logical addresses with 0 reserved for the Slot-0 controller.                                                                 |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operational<br>Registers: | See A32 Space.                                                                                                                                                                                            |

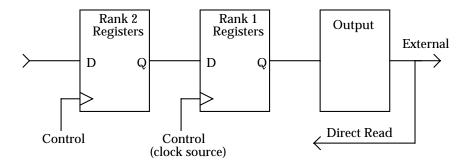

| Rank 1<br>Buffer:         | First level of double-buffered input circuit (or last stage of output circuit).                                                                                                                           |

| Rank 2<br>Buffer:         | Second level of double-buffered input circuit (or first stage of output circuit).                                                                                                                         |

| Resource<br>Manager:      | Also referred to as Resman. This software is made available by the manufacturer of the Slot-0 controller and is used to set logical addresses and Operational Registers of all the modules in the system. |

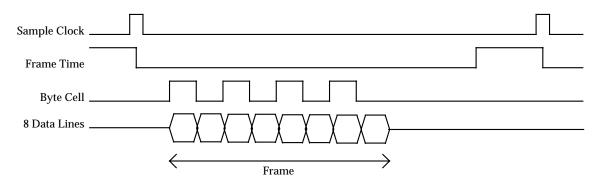

| Sample<br>Clock:          | Clock signifying the start of a data frame for use in Local Bus transfers. The sample clock is generated by the Local Bus Master.                                                                         |

# **INTRODUCTION**

The V387 module is a versatile, user configurable Input/Output device that contains up to 128 channels of discrete I/O. The V387 is configured through the use of modular, interchangeable mezzanine cards. There are four slots on the V387, each capable of handling 32 channels of discrete I/O. There are three types of I/O cards available: isolated input, output, and bidirectional. The logical convention is such that a contact closure or voltage present is interpreted as a logical "1". An additional socket is provided for an optional Digi-bus<sup>\*\*</sup> input or output interface.

There are two kinds of non-isolated cards for bidirectional transfers, a 32-channel single-ended TTL version, and a 16-channel differential version (RS-422 signal levels).

There are seven isolated input versions, 5Vdc, 12Vdc, 16Vdc, 24Vdc, 28Vdc, 48Vdc, and 120Vac. Each isolated input card has 16 channels. Switching threshold is approximately one-half the rated voltage. Each input has filtering for contact bounce suppression. The filter time constant is programmable from 5µs to 1s in 64 steps.

There are four 16-channel output cards. The output circuit are composed of reed relays, optical isolators, isolated AC switches, or SPDT (Form "C") contacts.

I/O data is double buffered, allowing the module to simultaneously sample or update all inputs or outputs, respectively. The device can be triggered from an external source, from the V387 itself, or from the VXI*bus*. The logical sense of the I/O data is user selectable. Pattern recognition compares incoming data to a pre-written data pattern and data mask on a continuous basis. A change-of-state indicator is also updated on a continuous basis. Either function can be used to generate a VXI*bus* trigger or an interrupt.

The V387 is a single-width, C-size, register-based, VXI*bus* module which takes advantage of many of the features of the VXI standard. The VXI C-size specification, while it uses the same bus specification as VME, provides some significant system level enhancements. These include the definition of 8 TTL and 2 ECL trigger lines, a 10MHz ECL clock for system timing, module ID line for geographic addressing and module identification, an analog summing bus, and a 12-line daisy-chained Local Bus. These portions of the VXI standard provide a solid basis for a comprehensive systems level approach.

#### VXI Trigger Lines

Eight of the pins on the P2 connector of the VXI*bus* are defined as TTL trigger lines. These open collector lines provide a wired-OR function that is suited to their use in communicating event information between modules.

A practical concept in using these lines is that of event sources and event sinks. Any one of several modules may generate an event on a specific trigger line, and one or more modules may be programmed to respond to this event, including the module which is the source of the event.

Examples of V387 event sources are change of state detection, pattern match detection, and frontpanel external trigger inputs. Examples of event sinks are transient capture triggers to initiate the capture and local storage of a data segment, and sample clocks to synchronize sampling of input signals or the output of DAC or digital data.

#### **System Configuration Validation**

One of the issues, particularly in larger systems, is ensuring that the proper modules with the proper options are installed and configured in the system. This is especially important when the current system configuration cannot be validated because of system size or physical access to areas in a distributed system. Verifying proper installation can be particularly frustrating when modules of the same type or model number can be configured with a number of internal options. Unfortunately, this is an increasingly common practice because of the high densities that can be achieved today and the relatively large card size of VXI. A related issue is the capability to identify and trace the history of specific modules within a larger system.

The VXI standard requires (or in some cases, suggests) that certain register conventions be followed. These register conventions partially address these issues. Standardized registers include the manufacturer ID assigned by the VXI Consortium, a device-type or model identifier, a serial number, and a version number or revision number for hardware and firmware.

An extension of this concept provides a module option identifier as well as some amount of userwriteable EEPROM. The EEPROM provides the capability to record in nonvolatile memory any option, calibration, or other module-specific information that may be important to system operation and/or maintenance. Since these registers are accessible by software, it is possible to develop software to verify system configuration at startup, as well as track modules for maintenance purposes.

#### **Private Digital Path, Digi-bus**

The VXI Local Bus provides 12 user-defined lines that are daisy-chained to adjacent modules. For digital signals, these lines provide a simple way to implement private data paths between system components that follow natural data flow, such as between an ADC and a digital signal processor

(DSP) and/or a large block of memory. In many applications, there is a requirement to perform FFTs, digital filtering, and signal averaging. Other applications include a need to store huge amounts of data.

The VXI Local Bus provides a convenient mechanism to implement a private digital bus (Digi-bus) for moving synchronous data between modular elements of the system. By using a private synchronous bus as opposed to the main VXI backplane bus, issues regarding bus contention and latency are avoided.

The Digi-bus is propagated from slot to slot by appropriate modules. Transfers of "frames" of data are synchronous with the clock line used to drive the Digital-In modules. The right-most "source" module is designated as the master. The master provides the time base for a frame of data as well as control and termination for the bus. One fixed length frame of data is generated for each tick of the designated clock. Frame length is determined at configuration time by software consistent with the source module capabilities and configuration. The clock "tick" serves as the beginning of a new frame. In a multi-source configuration each source module is configured by software to generate a selected number of data items per clock tick at a selected location in the frame. Each data source has pre-assigned locations within a frame to place data, and data sinks can extract data from known locations within a frame. In effect, each module is assigned a "time slot" for transferring its data. The Digi-bus supports multiple data sources as well as multiple data sinks. The left-most sink also terminates the bus.

Since a particular sink module may only require selected data from a frame or, in some cases, only every Nth sample, a data selection scheme must be provided. Digi-bus implements a simple bit map of the frame that selects data based on position within a frame.

The Digi-bus supports transfer rates up to 10 Mbytes/second (10MHz) with bus timing controlled by the designated bus master. The right-most (source) module serves as bus master and provides all necessary timing and control as well as termination. The left-most (sink) module also provides bus termination. Data flow is generally from right to left. The VXI Slot-0 controller is defined by the standard to be in the left-most slot. Since the Slot-0 is either a computer in its own right (smart controller) or connected to a computer, the possibility of passing digital Local Bus data directly to the

Slot-0 should not be precluded. In fact, Digi-bus options are available for KineticSystems Slot-0, the V160.

The unit of data on the Digi-bus is the 16-bit word. Data sources with more than 16-bit resolution are handled by a double word. When transferring data in the double word format, the first word is the least significant 16-bits followed by the most significant 16-bits.

#### V387 Data Register Organization

Figure 2. Input Data Register Diagram

There are three data registers on the V387. Consider the input circuit shown in figure 2. The Rank 1 and Rank 2 data registers act to double buffer the I/O, while the Direct Input Read register reads the input or output directly. Reading the Direct Input Read Register passes the present state of the inputs through Ranks 1 and 2, overwriting both registers. Rank 1 can store either the state of the inputs from the last read of the Direct Input Read Register, or the state of the inputs when last clocked by the selected clock source for the I/O card being used. Reading Rank 1 data overwrites Rank 2 data. Rank 2 stores the last data read, either from the Rank 1 Register or the Direct Input Read Register.

The register arrangement for an output-configured circuit is shown in figure 3. Reading the Direct Input Read Register for an output circuit yields the present state of the outputs, and does not affect the data stored in the Rank 1 and Rank 2 output registers. Writing data to Rank 2 stores the data in Rank 2. When strobed by the clock selected by the Clock Source Register, the data in Rank 2 then moves into the Rank 1 register. Writing to Rank 1 immediately overwrites the Rank 2 and Rank 1 registers and updates the outputs.

Figure 3. Output Data Register Diagram

#### Handshaking Organization

The Handshake Registers control the handshaking protocol for the bi-directional TTL card and the differential TTL card, allowing the V387 to communicate with external peripheral devices. These cards support three handshake signals not implemented on input- or output-only cards, the signals DATA STROBE OUT, ACKNOWLEDGE IN, and ERROR IN. Handshaking can be enabled or disabled through register control. With handshaking enabled, the DATA STROBE OUT line is asserted at the beginning of an I/O transfer. For the transfer to occur, the ACKNOWLEDGE IN line must be asserted by the external device. The ERROR IN line may also be asserted instead of the ACKNOWLEDGE IN line and the transfer will be aborted. Handshaking is used in both read and write cycles. With handshaking enabled for the card and no external ACKNOWLEDGE IN or ERROR IN signal received, transfers to the card's I/O locations will be aborted when the controller times-out the bus cycle. The maximum time the external device has to respond with an acknowledge or error signal is determined by the maximum bus cycle time of the controller. With handshaking disabled, an internal auto-acknowledge signal is generated to complete the I/O transfer.

#### UNPACKING AND INSTALLATION

At KineticSystems, static precautions are observed from production, test and packaging of the module. This includes using static-proof mats and wrist straps. Please observe these same precautions when unpacking and installing the module whenever possible.

The Model V387 is shipped in an anti-static bag within a Styrofoam packing container. Carefully remove the module from its static-proof bag and prepare to set the options to conform to the operating environment.

#### **Logical Address Switches**

The V387 represents one of the 255 devices permitted in a VXI*bus* system (Logical Address 0 is reserved for the Slot 0 device). The module is shipped from the factory with its address set for Logical Address 255. This address can be shared by multiple devices in a system that supports dynamic configuration. If the module is set for a Logical Address of 255 then the V387 will be dynamically configured by the Resource Manager. If the V387 is to be used in a system that does not support dynamic configuration, or in a system where static configuration of the module is desired, the Logical Address must be manually established. It is therefore the user's responsibility to ensure that no two modules are set to the same address. The Logical Address is set by manipulating eight rocker switches located under the access hole in the module's right-side ground shield (Refer to Figure 4).

FIGURE 4 - V387 SWITCH LOCATIONS

The eight switches represent a binary combination of numbers that range from zero to 255. Use a scribe or other appropriate instrument to set the Logical Address to the desired value.

The bit pattern for the A16 base address is shown below:

| 15 |   |           |          |          |          |         |         |         |         |   |   |   |   |   |   |  |

|----|---|-----------|----------|----------|----------|---------|---------|---------|---------|---|---|---|---|---|---|--|

| 1  | 1 | LA<br>128 | LA<br>64 | LA<br>32 | LA<br>16 | LA<br>8 | LA<br>4 | LA<br>2 | LA<br>1 | 0 | 0 | 0 | 0 | 0 | 0 |  |

Bits 15 and 14 are set to one (VXI defined).

Bits 13 through 6 are user selectable via the address switches LA128-LA1. Bits 5 through zero are set to "0" to indicate a block of 64 bytes.

For more information on switch settings, see "Programming Information"

#### **Module Insertion**

The V387 is a C-sized, single width VXI*bus* module. It requires 4.6 amps of +5 volt power, and 10 cubic feet per minute of air flow to maintain stability. Except for Slot 0, it can be mounted in any unoccupied slot in a C-sized VXI*bus* mainframe.

# CAUTION: TURN MAINFRAME POWER OFF WHEN INSERTING OR REMOVING MODULE

#### WARNING: REMEMBER TO REMOVE INTERRUPT ACKNOWLEDGE DAISY-CHAIN JUMPERS PRIOR TO INSERTING THIS MODULE IN THE BACKPLANE OR USE AN AUTOCONFIGURING BACKPLANE

To insure proper interrupt acknowledge cycles from the V387 module, the daisy-chain Interrupt Acknowledge jumper must be removed before the module is installed in a slot. Conversely, daisy-chain jumpers must be installed in any empty slot between the V387 and the Slot 0 Controller.

#### **Front Panel Information**

#### LEDs

Add Rec This LED turns on when V387's registers are being accessed (Address Received).

Failed This LED turns on when the V387 has failed or is executing its self-test.

#### Connectors

The V387 has four fifty-position SCSI-II type pin connectors on the front panel. Each connector, P3-P6, corresponds to a mezzanine card, C3-C6, respectively. Refer to each optional cards' description for the correct pinout assignments.

### FIGURE 5 - 50-POSITION SCSI-II PLUG

The connector pictured above is an example of the connectors used on the V387. The connector is shown with the pinout and position as indicated if viewed from the front panel.

# **Strap Options**

All straps on the V387 are for testing purposes only. They should remain in their factory configured position for proper operation.

FIGURE 6 - V387 CARD OUTLINES

г

# Mezzanine Card Front Panel Pinouts Table 1. Isolated Input Cards

| P300-300 16-Channel Isolated Input (5VDC) Pinout<br>P300-301 16-Channel Isolated Input (12VDC) Pinout<br>P300-302 16-Channel Isolated Input (24VDC) Pinout<br>P300-303 16-Channel Isolated Input (48VDC) Pinout<br>P300-304 16-Channel Isolated Input (120VAC) Pinout |                                     |    |                    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----|--------------------|--|--|--|

| Pin Number                                                                                                                                                                                                                                                            | Number Function Pin Number Function |    |                    |  |  |  |

| 1                                                                                                                                                                                                                                                                     | Channel 1 Signal                    | 26 | Channel 1 Return   |  |  |  |

| 2                                                                                                                                                                                                                                                                     | Channel 2 Signal                    | 27 | Channel 2 Return   |  |  |  |

| 3                                                                                                                                                                                                                                                                     | Channel 3 Signal                    | 28 | Channel 3 Return   |  |  |  |

| 4                                                                                                                                                                                                                                                                     | Channel 4 Signal                    | 29 | Channel 4 Return   |  |  |  |

| 5                                                                                                                                                                                                                                                                     | Channel 5 Signal                    | 30 | Channel 5 Return   |  |  |  |

| 6                                                                                                                                                                                                                                                                     | Channel 6 Signal                    | 31 | Channel 6 Return   |  |  |  |

| 7                                                                                                                                                                                                                                                                     | Channel 7 Signal                    | 32 | Channel 7 Return   |  |  |  |

| 8                                                                                                                                                                                                                                                                     | Channel 8 Signal                    | 33 | Channel 8 Return   |  |  |  |

| 9                                                                                                                                                                                                                                                                     | Channel 9 Signal                    | 34 | Channel 9 Return   |  |  |  |

| 10                                                                                                                                                                                                                                                                    | Channel 10 Signal                   | 35 | Channel 10 Return  |  |  |  |

| 11                                                                                                                                                                                                                                                                    | Channel 11 Signal                   | 36 | Channel 11 Return  |  |  |  |

| 12                                                                                                                                                                                                                                                                    | Channel 12 Signal                   | 37 | Channel 12 Return  |  |  |  |

| 13                                                                                                                                                                                                                                                                    | Channel 13 Signal                   | 38 | Channel 13 Return  |  |  |  |

| 14                                                                                                                                                                                                                                                                    | Channel 14 Signal                   | 39 | Channel 14 Return  |  |  |  |

| 15                                                                                                                                                                                                                                                                    | Channel 15 Signal                   | 40 | Channel 15 Return  |  |  |  |

| 16                                                                                                                                                                                                                                                                    | Channel 16 Signal                   | 41 | Channel 16 Return  |  |  |  |

| 17                                                                                                                                                                                                                                                                    | No Connection                       | 42 | No Connection      |  |  |  |

| 18                                                                                                                                                                                                                                                                    | No Connection                       | 43 | No Connection      |  |  |  |

| 19                                                                                                                                                                                                                                                                    | No Connection                       | 44 | No Connection      |  |  |  |

| 20                                                                                                                                                                                                                                                                    | Data Strobe In                      | 45 | Data Strobe In Rtn |  |  |  |

| 21                                                                                                                                                                                                                                                                    | No Connection                       | 46 | No Connection      |  |  |  |

| 22                                                                                                                                                                                                                                                                    | No Connection                       | 47 | No Connection      |  |  |  |

| 23                                                                                                                                                                                                                                                                    | No Connection                       | 48 | No Connection      |  |  |  |

| 24                                                                                                                                                                                                                                                                    | No Connection                       | 49 | No Connection      |  |  |  |

| 25                                                                                                                                                                                                                                                                    | No Connection                       | 50 | No Connection      |  |  |  |

| Table 2. Isolated Output Cards                                                                                                            |                   |            |                   |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|-------------------|--|--|--|

| P300-341 16-Channel Isolated Output Pinout<br>P300-342 16-Channel Reed Relay Output Pinout<br>P300-344 16-Channel AC Switch Output Pinout |                   |            |                   |  |  |  |

| Pin Number                                                                                                                                | Function          | Pin Number | Function          |  |  |  |

| 1                                                                                                                                         | Channel 1 Signal  | 26         | Channel 1 Return  |  |  |  |

| 2                                                                                                                                         | Channel 2 Signal  | 27         | Channel 2 Return  |  |  |  |

| 3                                                                                                                                         | Channel 3 Signal  | 28         | Channel 3 Return  |  |  |  |

| 4                                                                                                                                         | Channel 4 Signal  | 29         | Channel 4 Return  |  |  |  |

| 5                                                                                                                                         | Channel 5 Signal  | 30         | Channel 5 Return  |  |  |  |

| 6                                                                                                                                         | Channel 6 Signal  | 31         | Channel 6 Return  |  |  |  |

| 7                                                                                                                                         | Channel 7 Signal  | 32         | Channel 7 Return  |  |  |  |

| 8                                                                                                                                         | Channel 8 Signal  | 33         | Channel 8 Return  |  |  |  |

| 9                                                                                                                                         | Channel 9 Signal  | 34         | Channel 9 Return  |  |  |  |

| 10                                                                                                                                        | Channel 10 Signal | 35         | Channel 10 Return |  |  |  |

| 11                                                                                                                                        | Channel 11 Signal | 36         | Channel 11 Return |  |  |  |

| 12                                                                                                                                        | Channel 12 Signal | 37         | Channel 12 Return |  |  |  |

| 13                                                                                                                                        | Channel 13 Signal | 38         | Channel 13 Return |  |  |  |

| 14                                                                                                                                        | Channel 14 Signal | 39         | Channel 14 Return |  |  |  |

| 15                                                                                                                                        | Channel 15 Signal | 40         | Channel 15 Return |  |  |  |

| 16                                                                                                                                        | Channel 16 Signal | 41         | Channel 16 Return |  |  |  |

| 17                                                                                                                                        | No Connection     | 42         | No Connection     |  |  |  |

| 18                                                                                                                                        | No Connection     | 43         | No Connection     |  |  |  |

| 19                                                                                                                                        | No Connection     | 44         | No Connection     |  |  |  |

| 20                                                                                                                                        | No Connection     | 45         | No Connection     |  |  |  |

| 21                                                                                                                                        | No Connection     | 46         | No Connection     |  |  |  |

| 22                                                                                                                                        | No Connection     | 47         | No Connection     |  |  |  |

| 23                                                                                                                                        | No Connection     | 48         | No Connection     |  |  |  |

| 24                                                                                                                                        | No Connection     | 49         | No Connection     |  |  |  |

| 25                                                                                                                                        | No Connection     | 50         | No Connection     |  |  |  |

|                                                                                                                                           |                   |            |                   |  |  |  |

#### **Table 2. Isolated Output Cards**

|                | Table 3. Relay          | <b>Output Card</b> |                   |

|----------------|-------------------------|--------------------|-------------------|

| P300-343 16-Cl | nannel Form "C" Relay C | output Pinout      |                   |

| Pin Number     | Function                | Pin Number         | Function          |

| 1              | Channel 1 Signal        | 26                 | Channel 1 N.C.    |

| 2              | Channel 2 Signal        | 27                 | Channel 3 Signal  |

| 3              | Channel 3 N.C.          | 28                 | Channel 4 Signal  |

| 4              | Channel 5 Signal        | 29                 | Channel 5 N.C.    |

| 5              | Channel 6 Signal        | 30                 | Channel 7 Signal  |

| 6              | Channel 7 N.C.          | 31                 | Channel 8 Signal  |

| 7              | Channel 9 Signal        | 32                 | Channel 9 N.C.    |

| 8              | Channel 10 Signal       | 33                 | Channel 11 Signal |

| 9              | Channel 11 N.C.         | 34                 | Channel 12 Signal |

| 10             | Channel 13 Signal       | 35                 | Channel 13 N.C.   |

| 11             | Channel 14 Signal       | 36                 | Channel 15 Signal |

| 12             | Channel 15 N.C.         | 37                 | Channel 16 Signal |

| 13             | No Connection           | 38                 | Channel 1 N.O.    |

| 14             | Channel 2 N.C.          | 39                 | Channel 2 N.O.    |

| 15             | Channel 3 N.0.          | 40                 | Channel 4 N.C.    |

| 16             | Channel 4 N.O.          | 41                 | Channel 5 N.O.    |

| 17             | Channel 6 N.C.          | 42                 | Channel 6 N.O.    |

| 18             | Channel 7 N.O.          | 43                 | Channel 8 N.C.    |

| 19             | Channel 8 N.O.          | 44                 | Channel 9 N.O.    |

| 20             | Channel 10 N.C.         | 45                 | Channel 10 N.O.   |

| 21             | Channel 11 N.O.         | 46                 | Channel 12 N.C.   |

| 22             | Channel 12 N.O.         | 47                 | Channel 13 N.O.   |

| 23             | Channel 14 N.C.         | 48                 | Channel 14 N.O.   |

| 24             | Channel 15 N.O.         | 49                 | Channel 16 N.C.   |

| 25             | Channel 16 N.O.         | 50                 | No Connection     |

# Table 3. Relay Output Card

| Table 4. Bi-directional TTL Card |                           |               |                |  |  |  |  |  |  |  |  |  |

|----------------------------------|---------------------------|---------------|----------------|--|--|--|--|--|--|--|--|--|

| P300-380 32-Cl                   | nannel Bi-directional TTI | L Card Pinout |                |  |  |  |  |  |  |  |  |  |

| Pin Number                       | Function                  | Pin Number    | Function       |  |  |  |  |  |  |  |  |  |

| 1                                | Data Bit 1                | 26            | Data Bit 2     |  |  |  |  |  |  |  |  |  |

| 2                                | Data Bit 3                | 27            | Data Bit 4     |  |  |  |  |  |  |  |  |  |

| 3                                | Data Bit 5                | 28            | Data Bit 6     |  |  |  |  |  |  |  |  |  |

| 4                                | Data Bit 7                | 29            | Data Bit 8     |  |  |  |  |  |  |  |  |  |

| 5                                | Data Bit 9                | 30            | Data Bit 10    |  |  |  |  |  |  |  |  |  |

| 6                                | Data Bit 11               | 31            | Data Bit 12    |  |  |  |  |  |  |  |  |  |

| 7                                | Data Bit 13               | 32            | Data Bit 14    |  |  |  |  |  |  |  |  |  |

| 8                                | Data Bit 15               | 33            | Data Bit 16    |  |  |  |  |  |  |  |  |  |

| 9                                | Data Bit 17               | 34            | Data Bit 18    |  |  |  |  |  |  |  |  |  |

| 10                               | Data Bit 19               | 35            | Data Bit 20    |  |  |  |  |  |  |  |  |  |

| 11                               | Data Bit 21               | 36            | Data Bit 22    |  |  |  |  |  |  |  |  |  |

| 12                               | Data Bit 23               | 37            | Data Bit 24    |  |  |  |  |  |  |  |  |  |

| 13                               | Data Bit 25               | 38            | Data Bit 26    |  |  |  |  |  |  |  |  |  |

| 14                               | Data Bit 27               | 39            | Data Bit 28    |  |  |  |  |  |  |  |  |  |

| 15                               | Data Bit 29               | 40            | Data Bit 30    |  |  |  |  |  |  |  |  |  |

| 16                               | Data Bit 31               | 41            | Data Bit 32    |  |  |  |  |  |  |  |  |  |

| 17                               | Acknowledge In            | 42            | Error In       |  |  |  |  |  |  |  |  |  |

| 18                               | Data Strobe Out           | 43            | Data Strobe In |  |  |  |  |  |  |  |  |  |

| 19                               | Ground                    | 44            | Ground         |  |  |  |  |  |  |  |  |  |

| 20                               | Ground                    | 45            | Ground         |  |  |  |  |  |  |  |  |  |

| 21                               | Ground                    | 46            | Ground         |  |  |  |  |  |  |  |  |  |

| 22                               | Ground                    | 47            | Ground         |  |  |  |  |  |  |  |  |  |

| 23                               | Ground                    | 48            | Ground         |  |  |  |  |  |  |  |  |  |

| 24                               | Ground                    | 49            | Ground         |  |  |  |  |  |  |  |  |  |

| 25                               | Ground                    | 50            | Ground         |  |  |  |  |  |  |  |  |  |

## Table 4. Bi-directional TTL Card

| Pin Number | Function          | Pin Number | Function          |

|------------|-------------------|------------|-------------------|

| 1          | + Data Bit 1      | 26         | - Data Bit 1      |

| 2          | + Data Bit 2      | 27         | - Data Bit 2      |

| 3          | + Data Bit 3      | 28         | - Data Bit 3      |

| 4          | + Data Bit 4      | 29         | - Data Bit 4      |

| 5          | + Data Bit 5      | 30         | - Data Bit 5      |

| 6          | + Data Bit 6      | 31         | - Data Bit 6      |

| 7          | + Data Bit 7      | 32         | - Data Bit 7      |

| 8          | + Data Bit 8      | 33         | - Data Bit 8      |

| 9          | + Data Bit 9      | 34         | - Data Bit 9      |

| 10         | + Data Bit 10     | 35         | - Data Bit 10     |

| 11         | + Data Bit 11     | 36         | - Data Bit 11     |

| 12         | + Data Bit 12     | 37         | - Data Bit 12     |

| 13         | + Data Bit 13     | 38         | - Data Bit 13     |

| 14         | + Data Bit 14     | 39         | - Data Bit 14     |

| 15         | + Data Bit 15     | 40         | - Data Bit 15     |

| 16         | + Data Bit 16     | 41         | - Data Bit 16     |

| 17         | + Acknowledge In  | 42         | - Acknowledge In  |

| 18         | + Error In        | 43         | - Error In        |

| 19         | + Data Strobe In  | 44         | - Data Strobe In  |

| 20         | + Data Strobe Out | 45         | - Data Strobe Out |

| 21         | Ground            | 46         | Ground            |

| 22         | Ground            | 47         | Ground            |

| 23         | Ground            | 48         | Ground            |

| 24         | Ground            | 49         | Ground            |

| 25         | Ground            | 50         | Ground            |

# Table 5. Differential Card

#### **PROGRAMMING INFORMATION**

#### VMEbus/VXIbus Addressing

The V387 is classified according to the VXI specification as an extended register-based device, which means it has registers that occupy A16 and A32 space. The V387 contains Configuration Registers as required for VXI extended register based devices. The V387 also contains a set of Operational Registers to monitor and control the functional aspects of the device.

The Configuration Registers are located in A16 space and include the standard registers as well as additional general purpose registers. From these registers, information about the specific module can be read, the base address for the A32 registers can be controlled, and the interrupt level can be set. For example, by reading certain registers in A16 space, the following information about this module can be found just by knowing the module's logical address:

| KineticSystems |

|----------------|

| V387           |

| ZA11           |

| 20             |

| 1.0            |

| 1.0            |

|                |

In general, any configuration register can be accessed by simply knowing the module's logical address (set by the logical address switches) and the register's offset. The configuration registers are located in the upper 16 kilobytes of the A16 address range (C000<sub>16</sub> to FFFF<sub>16</sub>). The logical address switch settings or the contents of the Logical Address Register (see below) are mapped into address lines A6 through A13, establishing a base address for the module somewhere in the range of C000<sub>16</sub> to FFC0<sub>16</sub>. A complete list of the A16 registers and corresponding address offsets is available in the next section. The general formula for obtaining the A16 address of a register is:

$$A16\_Address = C000_{16} + (Logical\_Address \cdot 40_{16}) + Offset$$

#### **VXIbus Configuration Registers**

Configuration Registers are required by the VXI*bus* specification so that the appropriate levels of system configuration can be accomplished. The Configuration Registers in the V387 are offset from the base address. Note: the V387 only responds to these addresses if the Short Nonpriviledged Access (29<sub>16</sub>) or Short Supervisory Access (2D<sub>16</sub>) Address Modifier Codes are set for the backplane bus cycle. Table 6 shows the applicable Configuration Registers present in the V387, their offset from the base (Logical) address, and their Read/Write capabilities.

| A16 Offset                          | Read/Write<br>Capability | Register Name               |

|-------------------------------------|--------------------------|-----------------------------|

| 0016                                | Mixed                    | ID/Logical Address Register |

| 0216                                | Read Only                | Device Type Register        |

| 0416                                | Mixed                    | Status/Control Register     |

| 0616                                | Read/Write               | Offset Register             |

| 0816                                | Read Only                | Attribute Register          |

| 0A16                                | Read Only                | Serial Number High Register |

| 0C <sub>16</sub>                    | Read Only                | Serial Number Low Register  |

| 0E <sub>16</sub>                    | Read Only                | Version Number Register     |

| 10 <sub>16</sub> - 19 <sub>16</sub> | Read Only                | Reserved Registers          |

| 1A <sub>16</sub>                    | Read Only                | Interrupt Status Register   |

| 1C <sub>16</sub>                    | Mixed                    | Interrupt Control Register  |

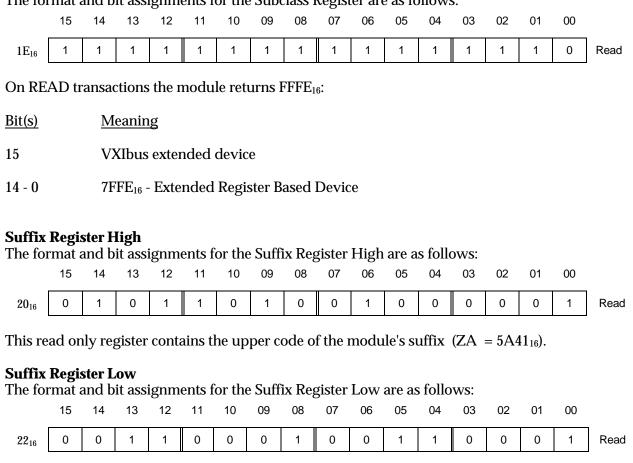

| 1E <sub>16</sub>                    | Read Only                | Subclass Register           |

| 2016                                | Read Only                | Suffix Register High        |

| 2216                                | Read Only                | Suffix Register Low         |

| 24 <sub>16</sub> - 3F <sub>16</sub> | Read/Write               | User Defined Registers      |

Table 6. Configuration Registers - A16 Space

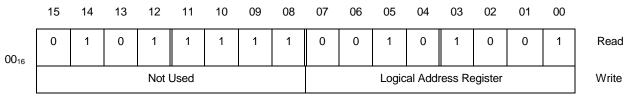

#### **ID/Logical Address Register**

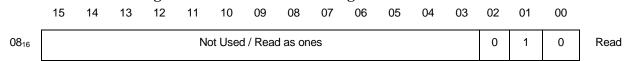

The format and bit assignments for the ID/Logical Address register are as follows:

On READ transactions the module returns 5F29<sub>16</sub>:

| <u>Bit(s)</u> | <u>Mnemonic</u>     | Meaning                                                |

|---------------|---------------------|--------------------------------------------------------|

| 15, 14        | Device Class        | This is an Extended Register-Based device.             |

| 13, 12        | Address Space Needs | This module requires the use of A16/A32 address space. |

| 11 - 00       | Manufacturer's ID   | 3881 (F29 <sub>16</sub> ) for KineticSystems.          |

For WRITE transactions, bits fifteen through eight are not used. A write to these bits has no effect on the V387. In Dynamically configured systems (i.e. the Logical Address switches set to a value of 255), bits seven through zero are written with the new Logical Address value obtained from the resource manager.

#### **Device Type Register**

The format and bit assignments for the Device Type register are as follows:

|                  | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |      |

|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|

| 02 <sub>16</sub> | 1  | 1  | 1  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | Read |

On READ transactions the module returns F387<sub>16</sub>:

| <u>Bit(s)</u> | <u>Mnemonic</u> | Meaning                                                                                                                           |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 15 - 12       | Required Memory | The V387 requires 64k bytes of additional memory space. (This is the minimum number of bytes that may be requested in A32 space.) |

| 11 - 0        | Model Code      | Identifies this device as Model V387 (387 <sub>16</sub> ).                                                                        |

Model V387-ZA11 **Status/Control Register** The format and bit assignments for the Status/Control register are as follows: 15 14 13 10 09 08 07 06 05 04 03 02 12 11 01 00 MODID 1 1 1 1 RDY PASS RST A32 1 1 1 1 1 1 SYS ENA INB 0416 Not Used SYS RST A32 INB ENA Bit(s) Mnemonic Meaning This bit is written with a "1" to enable A32 addressing and reset (to "0") to disable A32 addressing. **This bit <u>must</u> be set to "1" to** 15 A32 Enable (A32 ENA) allow access to the module's Operational Registers. Reads of this bit indicate its current state. This bit is reset to "0" on power-up or the assertion of SYSRESET\* 14 MODID\* This read only bit is set to a "1" if the module is <u>not</u> selected with the MODID line on P2. A "0" indicates that the device is selected by a high state on the P2 MODID line. 13 - 04 Not used. These bits will return all "1s" when read. Ignored when written. 03 A "1" indicates the successful completion of register Ready initialization. (RDY) 02 Passed A "0" indicates that the V387 has failed or is executing its (PASS) self-test. 01 Sysfail Inb. Writing a "1" to this bit disables the device from driving the (SYS INB) SYSFAIL\* line. Reads of this bit indicate its current state. 00 Reset Writing a "1" to this bit forces the device into the Soft Reset condition. While in the Soft Reset state, the module will only allow access (RST) to its Configuration Registers. Writing a "0" to this bit will then force the module to begin executing its Self Test. This bit must be cleared along with the Passed and Ready bits set before any access to the Operational

Read

Write

#### **Offset Register**

The format and bit assignments for the Offset register are as follows:

Registers is allowed.

|      | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |                |

|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----------------|

| 0616 | A31 | A30 | A29 | A28 | A27 | A26 | A25 | A24 | A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 | Read/<br>Write |

After SYSRESET\* and prior to self-test, all bits are set to "0". Otherwise a write defines the base address of the device's operational registers.

#### **Attribute Register**

The format and bit assignments for the Attribute Register are as follows:

#### On READ transactions the module returns FFFA<sub>16</sub>

| Bit(s)  | <u>Mnemonic</u> | Meaning                                                                         |

|---------|-----------------|---------------------------------------------------------------------------------|

| 15 - 03 | Not used        | A write to these bits has no effect. A read of these bits will return all "1s". |

| 02      | Intr Control    | A zero indicates that the V387 has Interrupt Control capability.                |

| 01      | Intr Handler    | A one indicates that the V387 does not have Interrupt Handler capabilities.     |

| 00      | Intr Status     | A zero indicates that the V387 does have an Interrupt Status register.          |

#### **Serial Number High Register**

The format and bit assignments for the Serial Number High Register are as follows:

|                  | 15   | 14   | 13   | 12   | 11   | 10   | 09   | 08   | 07   | 06   | 05   | 04   | 03   | 02   | 01   | 00   |      |

|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 0A <sub>16</sub> | SN31 | SN30 | SN29 | SN28 | SN27 | SN26 | SN25 | SN24 | SN23 | SN22 | SN21 | SN20 | SN19 | SN18 | SN17 | SN16 | Read |

This read only register contains the upper code of the module's serial number.

#### **Serial Number Low Register**

The format and bit assignments for the Serial Number Low Register are as follows:

|                  | 15   | 14   | 13   | 12   | 11   | 10   | 09   | 08   | 07   | 06   | 05   | 04   | 03   | 02   | 01   | 00  |      |

|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|------|

| 0C <sub>16</sub> | SN15 | SN14 | SN13 | SN12 | SN11 | SN10 | SN09 | SN08 | SN07 | SN06 | SN05 | SN04 | SN03 | SN02 | SN01 | SN0 | Read |

This read only register contains the lower code of the module's serial number.

#### Version Number Register

The format and bit assignments for the Version Number Register are as follows:

|                  | 15   | 14            | 13              | 12    | 11 | 10           | 09             | 08  | 07   | 06            | 05 | 04    | 03 | 02 | 01               | 00  |      |

|------------------|------|---------------|-----------------|-------|----|--------------|----------------|-----|------|---------------|----|-------|----|----|------------------|-----|------|

| 0E <sub>16</sub> | Firm | ware N<br>Nun | lain Ve<br>nber | rsion | Fi | mware<br>Nun | Revisi<br>nber | ion | Hard | ware N<br>Nun |    | rsion | Ha |    | e Revisi<br>nber | ion | Read |

On READ transactions the module will return the revision level of its hardware and firmware:

| <u>Bit(s)</u> | <u>Mnemonic</u>              | <u>Example</u> |

|---------------|------------------------------|----------------|

| 15 - 12       | Firmware Main Version Number | 116            |

| 11 - 08       | Firmware Revision Number     | 016            |

| 07 - 04       | Hardware Main Version Number | $1_{16}$       |

| 03 - 00       | Hardware Revision Number     | 016            |

#### Address locations 10<sub>16</sub> - 19<sub>16</sub> are reserved

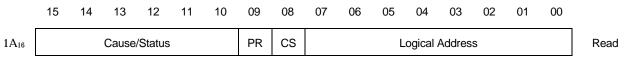

#### **Interrupt Status Register**

The format and bit assignments for the Interrupt Status Register are as follows:

A read of this register will clear the status bit(s) which generated the interrupt.